- STMicroelectronics Community

- Product forums

- Power management

- LED1642GW: Does it matter if the Latch (LE) signal...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LED1642GW: Does it matter if the Latch (LE) signal is shifted within one word?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-13 5:42 AM

Hello,

according to the datasheet of the LED1642 driver, the LE signal value is defined by the number of CLK rising edges when the LE is 1.

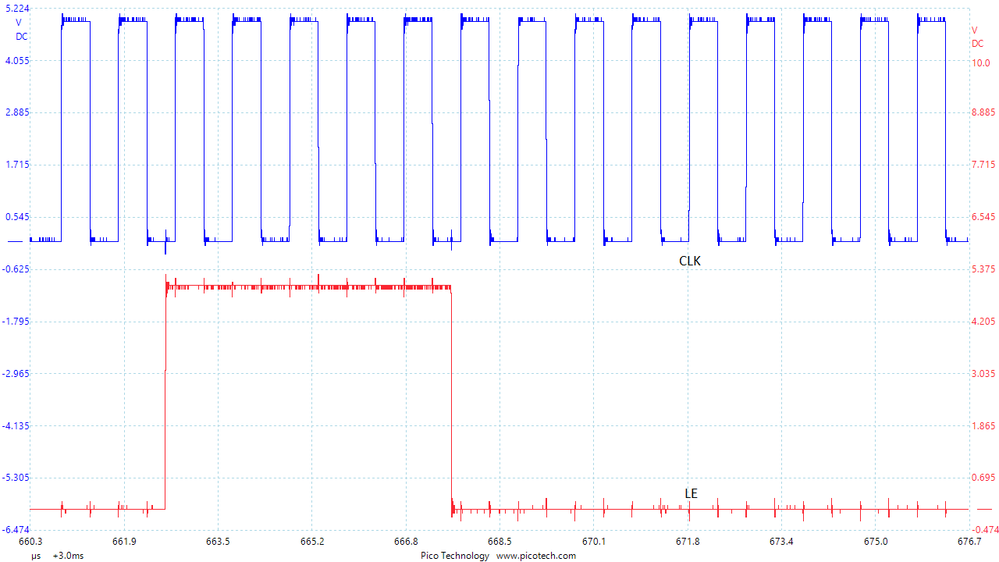

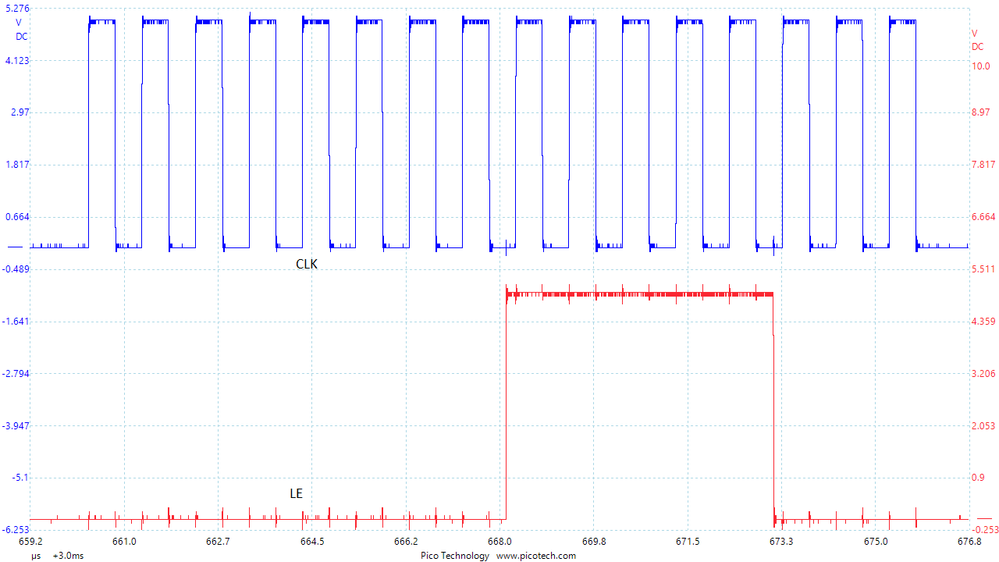

In the datasheet, the figures always show LE signals which are aligned to the first rising clock edge of a new data signal (SDI) (like it is shown in the attached figure).

Is this a requirement we need to meet when implementing a driver? Is it valid, when the LE signal is high for a specified number of clock rising edges in the middle of a data signal block (16 bit)?

best regards

- Labels:

-

Motor Control Hardware

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-21 8:25 AM

Does it matter?

The pictures show 16 clk - high signals, while the LE signal is high for 5 times on each picture. Is this valid?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-12-15 4:54 AM

push

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-11 11:30 PM

Do I have to move this topic to somewhere else?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-12 6:40 AM

These are primarily engineer-to-engineer forums, not a way to access ST's FAEs, so getting answers is somewhat reliant on other sharing similar interests or problems.

There is an online support request form, and this might yield some answers from their internal FAQ and support ticket system.

For engineering support contact your local sales office.

Up vote any posts that you find helpful, it shows what's working..

- STM32H503 – ADC trigger shifting from OFF midpoint at duty > 50% in center-aligned complementary PWM in STM32CubeIDE (MCUs)

- STM32L476 — Stable phase shift between TIM1 and TIM8 for DAB converter in STM32 MCUs Products

- VL53L8CX SPI on ESP32-S3: vl53l8cx_init() always fails on a Chinese AliExpress module in Imaging (sensors)

- Generate 2 PWMs with same frequency & duty, 90 degree phase shift, using one timer in STM32 MCUs Products

- Motor will stop after ramp p in STM32 MCUs Motor control