CMU - FMPLL clock reference values

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-19 1:02 AM

Hello everyone,

I'm working with SPC56EL60L3 and SPC5Studio v5.0.

I'm not sure I get how does the CMU_0 FMPLL clock monitoring work.

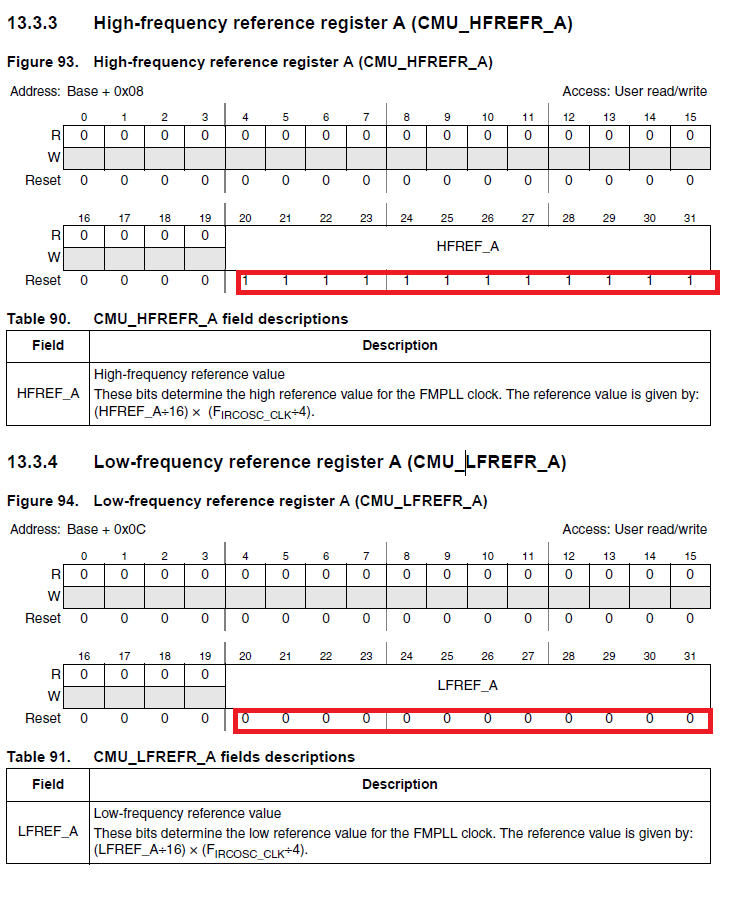

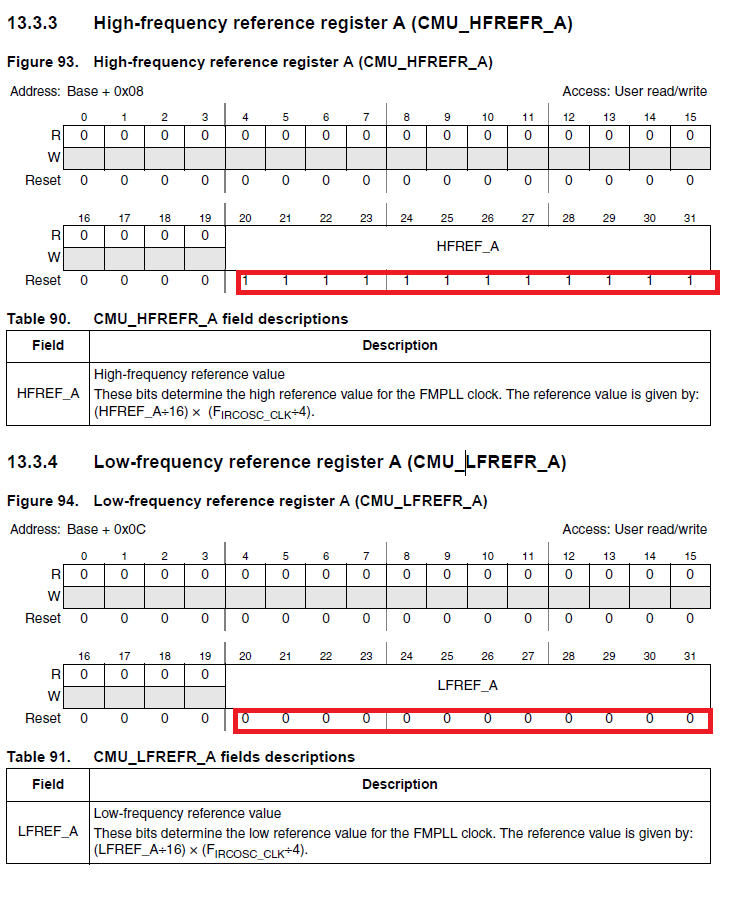

Reading the user manual (RM0032) at page 277 13.3.3 and 13.3.4, I've found some details on the CMU_HFREFR_A and CMU_LFREFR_A registers, but I have some questions.

First question: when is the FMPLL clock checked? Whwnever I start the CMU by setting the SFM bit in the CSR register?

Second question:

Table 90 says: These bits determine the high reference value for the FMPLL clock. The reference value is given by: (HFREF_A÷16) × (FIRCOSC_CLK÷4).

Table 90 says:

These bits determine the low reference value for the FMPLL clock. The reference value is given by: (LFREF_A÷16) × (FIRCOSC_CLK÷4).HFREF and LFREF are the contents of the two register, but what is FIRCOSC_CLK? Is it a predefined value or the content of a register, or what?

Thank you.

Regards

Alessandro

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-09 7:46 AM

Hello Alessandro ,

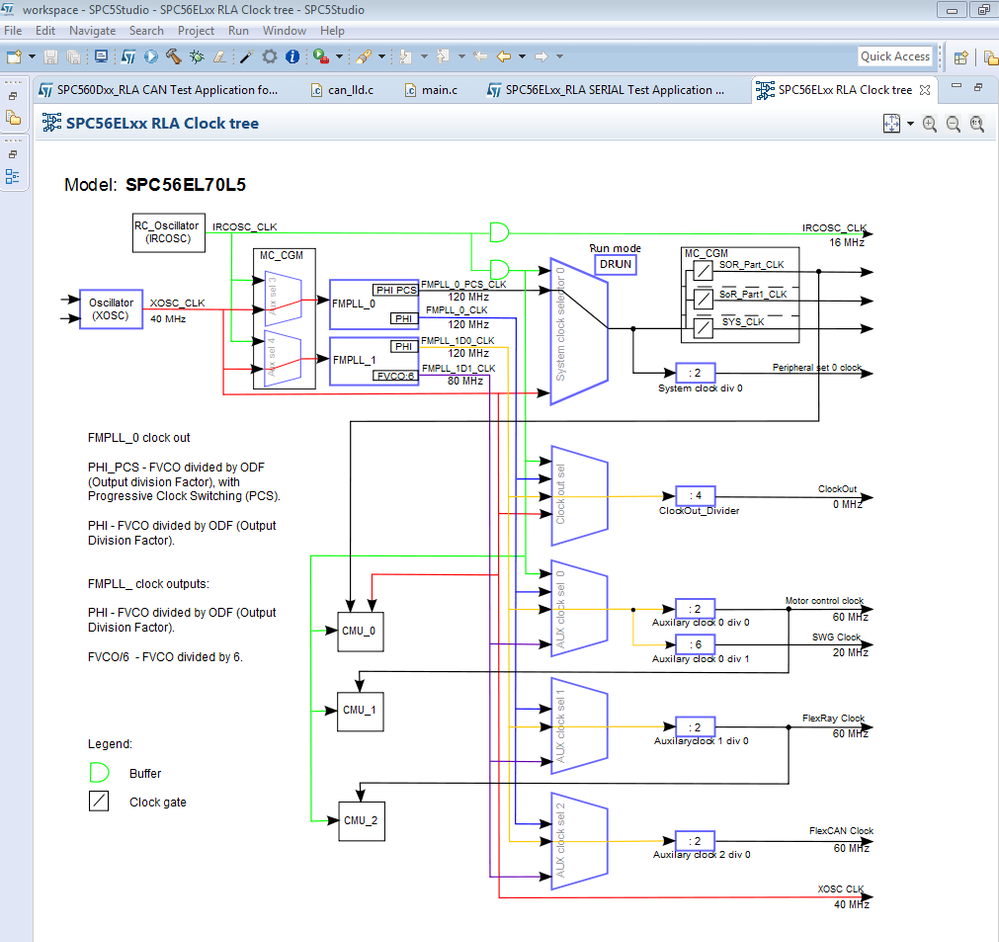

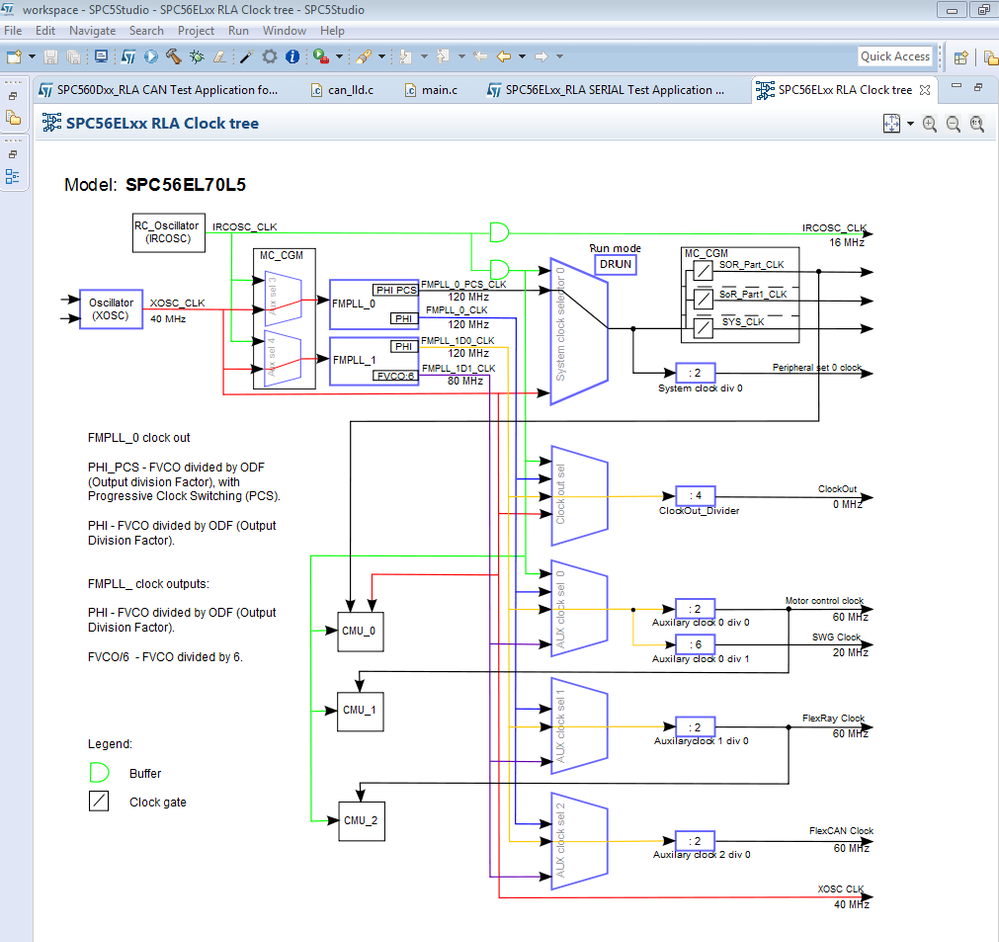

Do not hesitate to use the Clocktree wizard (cf screenshot) relative to

SPC56EL60L3 (cf RLA Application)

FIRCOSC_CLK is

The internal RC oscillatorit has a nominal frequency of 16 MHz.

The predefined value should be the reset values (cf below)

Best Regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-09 7:46 AM

Hello Alessandro ,

Do not hesitate to use the Clocktree wizard (cf screenshot) relative to

SPC56EL60L3 (cf RLA Application)

FIRCOSC_CLK is

The internal RC oscillatorit has a nominal frequency of 16 MHz.

The predefined value should be the reset values (cf below)

Best Regards

Erwan