- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- Not able to communicate device(STEVAL-IDP003V1) to...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Not able to communicate device(STEVAL-IDP003V1) to Master(STEVAL-IDP004V1)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-29 04:08 AM

Hi All,

I am using ST Master Evaluation Board(STEVAL-IDP004V1) and a device (STEVAL-IDP003V1).

I am trying to send some data from the master to device and it is succeeded.

"i am having problem in reception from the device to master". From the device side i am sending some data and that is a correct data(observed using logic analyzer at slave TX). when i am trying to receive at master side i am receiving a garbage.

Test setup:

1) Enabled L+ line

2) configured the Device in Transmit Mode.

3)Configured the Master in Reception Mode.

4) programmed the device to send some data for every 2 seconds.

5) programmed the master to receive the data upon an interrupt is received.

6) Kept a break point in reception callback function and observing the data received.

Observation:

Since i am receiving a garbage data over UART i tried to read the status register and i got value as "0x80" . For the same i have seen the data sheet and observed that "PO" bit is getting set.

My input power supply to the master evaluation board is 24V and the same observed on the "L+" line.

Could you Please Help me to resolve this issue.

Any Help would be appreciated.

Thanks in Advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-30 07:59 AM

Hi @SNAGU.1 ,

I checked internally with our experts of this evaluation kit and here below is the feedback I received.

The PO bit of the status register is often triggered during the power up of the device and can be reset only after a read current of the L6360 transceiver, so, if you firmware don't include a read at startup, it is normal that you will read it.

Moreover, if the bit is set also after a first reset of the Status register, you should verify the behavior of L+ in steady state and during the communication active.

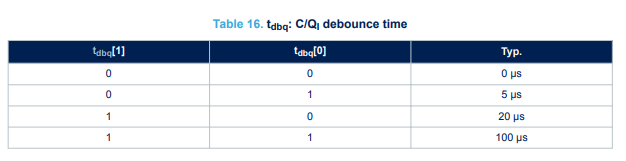

As regard the read error, if the master is set in receiver condition you should control the debounce time that you have selected depending on the baudrate, because if it is incorrect the L6360 will filter the incoming data frame.

You can run a test setting the debounce (tdbq bit) at Zero so that you don't have any filtering during the reception phase.

As far as I understand, it seems you verified the frame on device side on the pin TX of the uC.

Could you verify also the frame on the bus to understand if also the L6362A is correctly configured in transmission?

How are you managing the synchronization between the master and the device?

Thanks for a feedback,

-Eleon

- Sensor hub problems with LSM6DSV32X breakout, how to configure properly? in MEMS (sensors)

- The standby power consumption of the VL53L1X-SATEL far exceeds the value stated in the datasheet in Imaging (sensors)

- STM X-Nucleo-53L7A1 with Nucleo-F401RE does not work in Imaging (sensors)

- Challenges with LPS22DF: VDD_IO and VDD Interaction Causing I²C Issues in MEMS (sensors)

- Free Fall and Blue SDK in MEMS (sensors)