- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- Re: LSM6DSL FIFO Continuous mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LSM6DSL FIFO Continuous mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-01 08:11 AM

Hello,

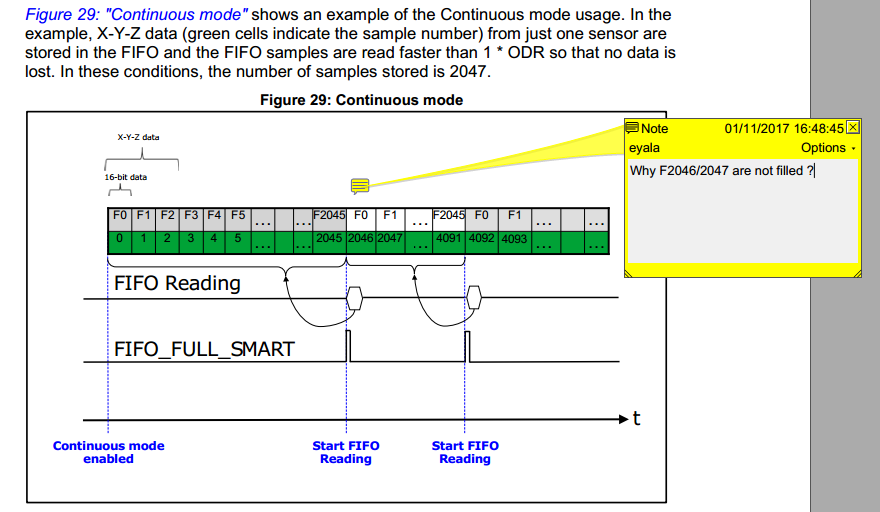

- The app note (pg 98) show an example to FIFO continuous mode.Looking at figure 29 it seem that the FIFO restart filling from F0 ('first' memory location) once read cycle begins.Is this the case? Shouldn't the FIFO fill to its last address (2047) and only than wrap around to F0 ?

- Does FIFO_FULL_SMART being set when FIFO fills to specific address (F2045), or is it triggered whenever the FIFO is about to be filled regardless where FIFO head is ?for instance - Assume sampling only Acc & Gyro (datasets 1&2), setting the FIFO threshold to (e.g.) FTH=20(decimal) and set

STOP_ON_FTH=1 bit.

Will the FIFO wrap around to 0 at address 19 ?Will FIFO_FULL_SMART be triggered initially when F17 is written ?Now the MCU reads F0-F8 (only), and the FIFO keeps filling F18, F19, F0, F1... will the next trigger of FIFO_FULL_SMART will be when writing to F6 (after writing the following datasets: DS1->F18/F19/F0, DS2->F1/F2/F3, DS1->F4/F5/F6) ?

Thanks

- Labels:

-

INEMO-Inertial Modules

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-02 11:48 PM

Hello Eyal,

Ad 1: Actually FIFO doesn't RESTART filling, it just keeps filling from the FIRST EMPTY slot, not necessarily from F0. But since the read cycle in this example is so fast that it reads the WHOLE FIFO in less then 1*ODR which means before any single data comes, the FIFO starts writing from first empty F0 slot even if it seems that writing to F2046 (which is also empty) would logically follow.

Ad 2: FIFO_FULL_SMART is set when the FIFO is going to be filled to the allowed top (either full or using STOP_ON_FTH) within NEXT dataset storage regardless where FIFO head is. Basically you don't care about

theslots, all you need to know is the number of samples currently stored in FIFO and the pattern to understand what data you get during next read. That's it.Best regards,

Petr- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-06 08:44 AM

Thanks Petr.

What happens if the MCU does not empty the FIFO within 1*ODR ?

Lets say the that FIFO is set to trigger an interrupt (FTH) when its ~halfway full (300 Acc+Gyro samples = F0-F1799).

The MCU empties the FIFO slower than 1*ODR so by the time the next sample arrives only 100 samples were read (F0-F599).

The FIFO now has two empty regions F0-F599 & F1800-4095.

Where the next samples would be written to: F1800 or F0 ?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-07 03:54 AM

Hi Eyal,

Next sample would be written to F0 but as I said you don't ever have to care about the position, just read the register with actual number of stored samples, create the cycle in which you read the actual pattern and sample, sort and store your data and once you finish this cycle wait for another interrupt (which in you 'slower reading' case will come sooner than the very first one, because during reading new samples have been stored to the FIFO) and restart the whole reading procedure.

I suggest you to download the

http://www.st.com/en/embedded-software/x-cube-mems-xt1.html

package from ST web which contains a few examples of FIFO usage. Even if you don't have any of supported Nucleo and MEMS Shield boards you can still at least inspire yourself by the open source code which ST shares for free.Best regards,

Petr- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-07 06:17 AM

You're welcome.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-07 06:23 AM

Hi Petr,

Understood. Thanks for your prompt reply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-08 10:51 PM

Hi Eyal,

I'm sorry I just realized I answered your very last question incorrectly. Correct and of course logical answer is that next samples would be written to F1800. FIFO buffer is a circular array always pointing to the oldest 16-bit word stored in the FIFO (it's basically the First-In-First-Out definition). Sorry for that.

Best regards,

Petr- LIS2MDL BDU only works for 3 axis independent readouts in MEMS (sensors)

- Interrupt mode. How to Adjust Calibration of LIS2MDL Sensor for Temperature Variations? in MEMS (sensors)

- LM6S3TR device FIFO pattern incorrect in MEMS (sensors)

- Generating interrupts from VL53L0X pin GPIO1 in Imaging (sensors)

- LSM6DSV32X Gyroscope Artifacts in MEMS (sensors)