Any way to detect the overflow of FIFO inside of the board stevalmki109v3 which has lsm6dsr.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-22 10:39 PM

I'm trying to get maximum data rate (ODR=6.66KHZ) of the LSM6DSR with using STEVALMKI109v3 and my own code running on windows 10 laptop. Unfortunately, I couldn't get reached to the speed. it was about 6.56KHZ. The RX buffer on laptop side is good in shape and well enough. And there's no overflow events according to the buffer monitoring.

Are there any way to detect the overflow events or read/check the FIFO status of STEVAL-MKI109v3 ?

Thank you

- Labels:

-

INEMO-Inertial Modules

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-23 7:41 AM

Hi @晃次 浅�? ,

Just a question for understanding if it is not a communication speed related issue: if you run the LSM6DSR ad ODR 3.33kHz, do you face the same problem?

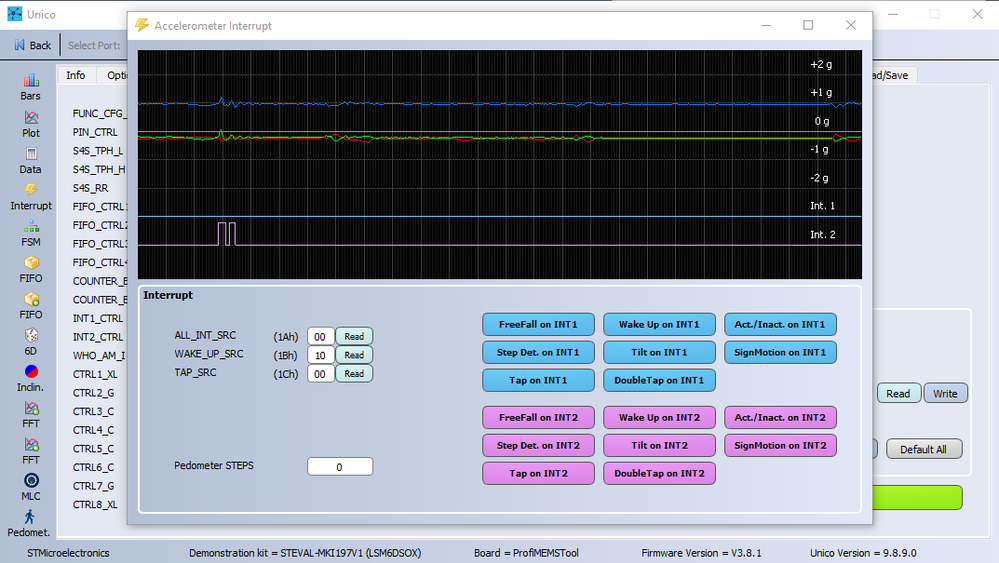

About the overflow event, you can detect it by reading (in polling mode) the FIFO_ OVR_IA bit FIFO_STATUS2 (3Bh), Otherwise, It is possible to route for example the FIFO_WTM_IA flag of FIFO_CTRL2 (08h) to the INT1 pin by writing in register INT1_CTRL (0Dh)(INT1_FIFO_TH) = '1' or to the INT2 pin by writing in register INT2_CTRL (0Eh)(INT2_FIFO_TH) = '1'. Then you can plot it on the Unico-GUI interrupt panel.

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-27 8:52 PM

Hi Eleon,

Thanks a lot for the idea to verify it and sorry for late my reply.

I will check and test based on your idea and put my feed back here soon.

Koji

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-29 5:42 AM

Here's the result of my experiment. I'm still facing same problem in various conditions as below.

Now, I'm wondering this number is within possible internal oscillators timing accuracy.. just my guess, not sure.

What do you think about it?

For the interruption of FIFO OVF or FULL, none of pin interruption at both INT1 and INT2 were observed.

I might be wrong. Please kindly review below instruction at (2). I sent those command before sending '*start' command to the board.

(1) Time measurement with various ODR mode and durations.

To minimize the effect of clock and timing accuracy on my laptop, the data from steval were captured with various durations(100sec,1000sec).

at room temperature about 20 degC, # of boards = 1 set.

environment: Ubuntu 18 Desktop

---

ODR setting = 416Hz(typ)

a) duration = 100sec

Measured data rate = 413.53Hz (-0.59% of typical)

Actual duration = 99.90 sec

# of captured samples = 41,312

b) duration = 1,000sec

Measured data rate = 412.795Hz (-0.77% of typical)

Actual duration = 999.843 sec

# of captured samples = 412,730

---

ODR setting = 833Hz(typ)

a) duration = 100sec

Measured data rate = 827.06Hz (-0.71% of typical)

Actual duration = 99.897 sec

# of captured samples = 82,621

b) duration = 1,000sec

Measured data rate = 825.575Hz (-0.89% of typical)

Actual duration = 999.886 sec

# of captured samples = 825,481

---

ODR setting = 1660Hz(typ)

a) duration = 100sec

Measured data rate = 1654.115Hz (-0.35% of typical)

Actual duration = 99.901 sec

# of captured samples = 165,247

b) duration = 1,000sec

Measured data rate = 1651.131Hz (-0.53% of typical)

Actual duration = 999.801 sec

# of captured samples = 1,650,803

---

ODR setting = 1660Hz(typ)

a) duration = 100sec

Measured data rate = 1654.115Hz (-0.35% of typical)

Actual duration = 99.901 sec

# of captured samples = 165,247

b) duration = 1,000sec

Measured data rate = 1651.131Hz (-0.53% of typical)

Actual duration = 999.801 sec

# of captured samples = 1,650,803

---

ODR setting = 3330Hz(typ)

a) duration = 100sec

Measured data rate = 3308.201Hz (-0.65% of typical)

Actual duration = 99.900 sec

# of captured samples = 330,491

b) duration = 1,000sec

Measured data rate = 3302.276Hz (-0.83% of typical)

Actual duration = 999.901 sec

# of captured samples = 3,301,948

---

ODR setting = 6660Hz(typ)

a) duration = 100sec

Measured data rate = 6616.404Hz (-0.65% of typical)

Actual duration = 99.807 sec

# of captured samples = 660,368

b) duration = 1,000sec

Measured data rate = 6604.516Hz (-0.83% of typical)

Actual duration = 999.837 sec

# of captured samples = 6,603,444

(2) FIFO mode setting

Sending below commands for the board initialization in every test.

*stop

*setdb194v1

*Zoff

To set desired mode, wrote sequentially below values with below order.

1. *w0D10 as INT1_CTRL, set INT1_FIFO_OVR

2. *w0E20 as INT2_CTRL, set INT2_FIFO_FULL

3. *w0A06 as FIFO_CTRL4, set FIFO_MOD = 110b Continous mode

4. *w10A4 as CTRL1_XL

5. *w11AC as CTRL2_G

and wait for 800 msec

Then, send '*start' to start capturing.

Thank you,

Koji

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-29 8:12 AM

Hi @晃次 浅�? ,

>> Now, I'm wondering this number is within possible internal oscillators timing accuracy... just my guess, not sure. What do you think about it?

I confirm that the values of the actual ODRs you are measuring are ok and are expected to be in a range of variation of +-1% for low ODRs and of +-3% at higher ODRs, although this value is not specified in the datasheet.

>> For the interruption of FIFO OVF or FULL, none of pin interruption at both INT1 and INT2 were observed. I might be wrong. Please kindly review below instruction at (2). I sent those command before sending '*start' command to the board.

I would suggest you to set the interrupt pins after the FIFO mode setting. Then you can try to read the FIFO_OVR_LATCHED bit of the FIFO_STATUS2 register before starting a new FIFO reading, to check if you are not just missing the INT1_FIFO_OVR for some reason.

You can also check the C file multi_read_fifo_simple.c for a complete overview on the register settings for the FIFO configuration of the LSM6DSR.

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-02 1:14 AM

Hi @Eleon BORLINI

Thanks a lot for the info. Understood and appreciated. I will check out the C file above and try it on my system.

Here's my different aspect of checking FIFO overflow.

Is it possible to capture the step counter value generated by IMU sensor and get it through the evaluation board?

My current application would be affected by the discontinuity of data stream from IMU sensor. It would be also perfect to me if my system is able to alarm the data discontinuity to my operators if it happened.

Thanks again,

Koji