- STMicroelectronics Community

- Product forums

- Interface and connectivity ICs

- Re: Migrating from SPBTLE_RF to SPBTLE-1S

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Migrating from SPBTLE_RF to SPBTLE-1S

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-14 03:11 PM

Customer would like to migrate from SPBTLE_RF to SPBTLE-1S. Are they pin compatible, or any app notes or other documents covering this migration. Customer is looking to migrate to gain BLE 4.2 support.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-15 07:23 PM

SPBTLE-RF and SPBTLE-1S are not pin compatible.

In fact, they have different pin counts.

It is because SPBTLE-RF is based on BlueNRG-MS, which is a BLE transceiver,

SPBTLE-1S, in comparison, is based on BlueNRG-1, which is an SoC including a MCU and a BLE transceiver.

If you would like to make SPBTLE-1S act like a SPBTLE-RF,

please flash it with the DTM (SPI one) firmware, and connect to the host processor through the SPI pins.

Please refer to DT0121 - How to configure the BlueNRG-1 and BlueNRG-2 devices in network coprocessor mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-16 06:34 AM

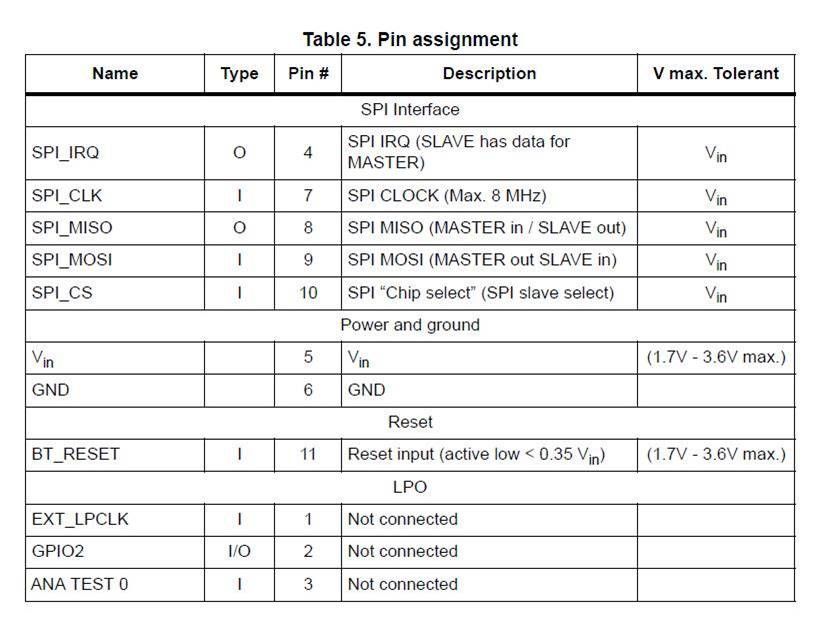

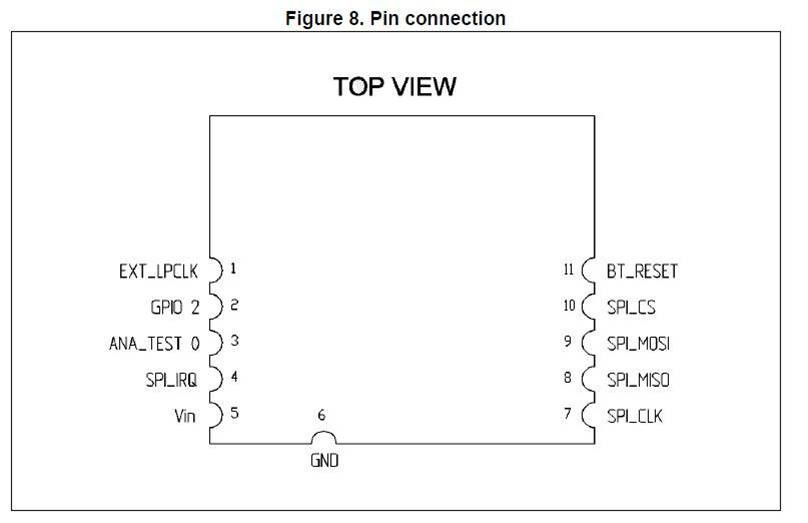

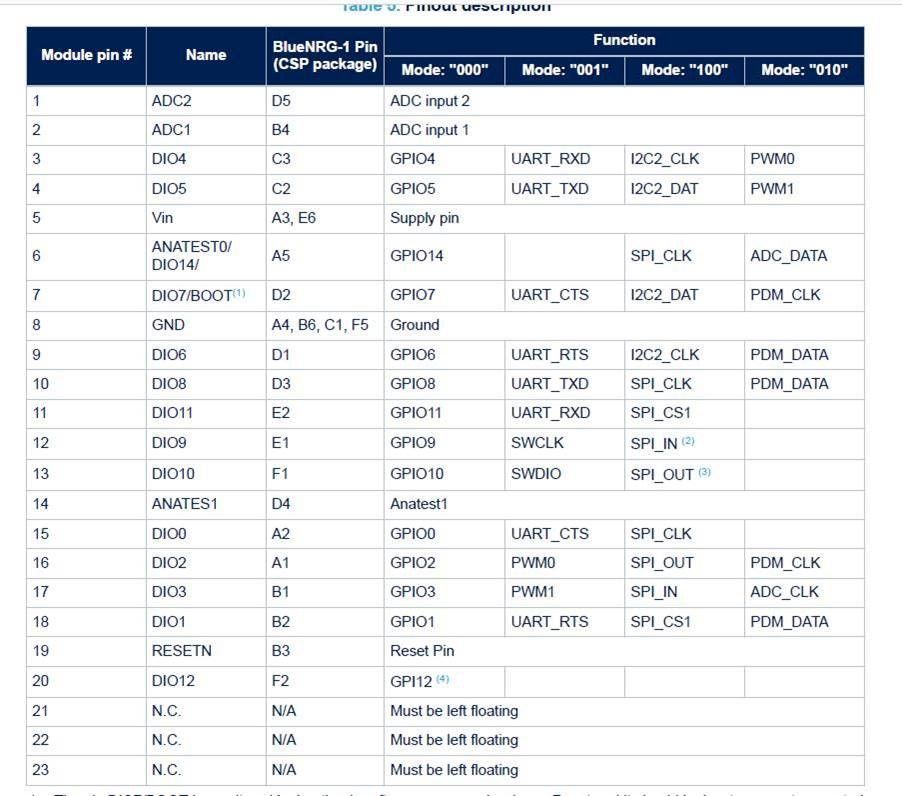

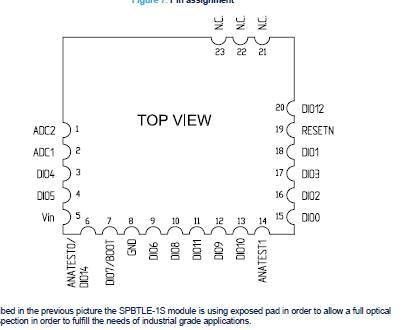

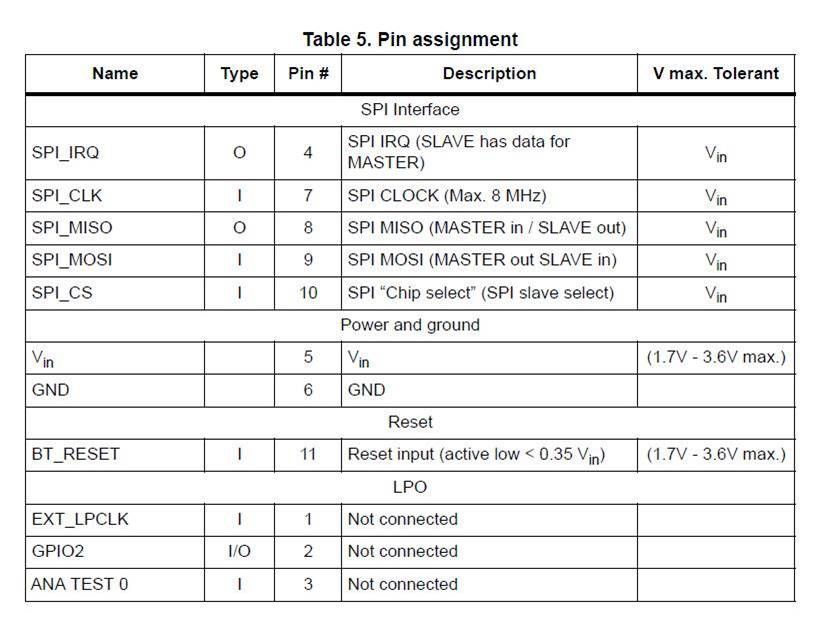

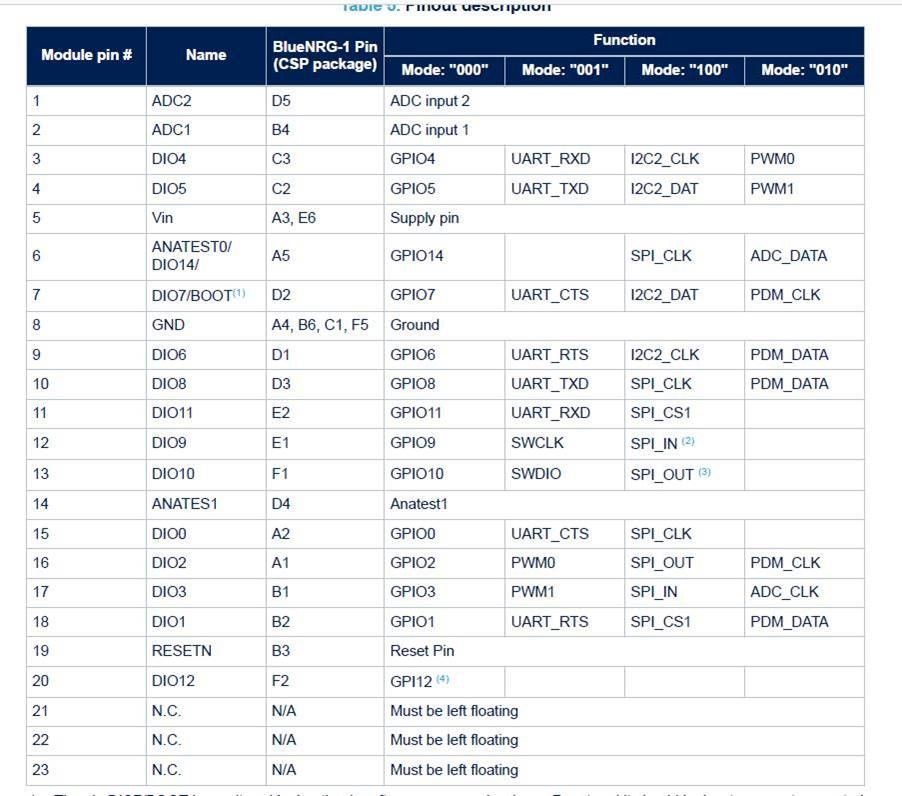

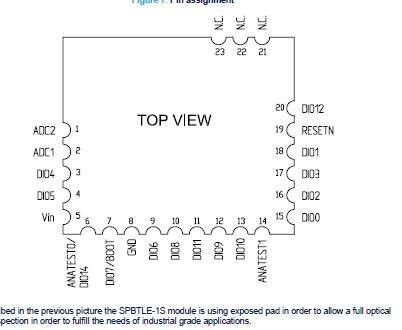

Yes they have different pin counts but the SPBTLE-RF is a subset of the SPBTLE-1S when the SPBTLE-1S is in the SPI mode (mode "100"). The only issue seems to be pin 4, SPI_IRQ.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-21 01:14 PM

Yes they have different pin counts but the SPBTLE-RF is a subset of the SPBTLE-1S when the SPBTLE-1S is in the SPI mode (mode "100"). The only issue seems to be pin 4, SPI_IRQ.

You mention "If you would like to make SPBTLE-1S act like a SPBTLE-RF,

please flash it with the DTM (SPI one) firmware, and connect to the host processor through the SPI pins."

Does this address the pin difference. The tables for the "1S" do not show a SPI-IRQ output on pin 4, but instead show it as I2C_DAT,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-26 06:36 PM

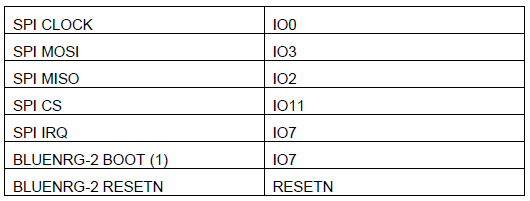

By default, SPI IRQ would be mapped to IO7.

The table of default pins used for SPI interface has been described in

DT0121 - How to configure the BlueNRG-1 and BlueNRG-2 devices in network coprocessor mode

https://www.st.com/resource/en/design_tip/dm00547290.pdf

Feel free to modify it according your needs.

In DTM project, hw_config.h line 54:

#define SPI_IRQ_PIN GPIO_Pin_7- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-27 08:25 AM

OK, but for the SP BTLE_1S, pin 4 on the module is I2C2_DAT. What pin is that routed to the BLUENRG. I guess I would need to redefine the SPI_IRQ_PIN to that location used by I2C2_DAT to bring the SPI_IRQ_PIN out of the module. I guess I can download the project to see it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-27 08:47 AM

For clarification, for the SPBTLE-RF module, is the BLUENRG programmed in the network coprocessor mode. So that for the SPBTLE-1S, if we program it for this same mode, with the pinout changes to bring the SPI_IRQ pin out pin 4 of the package, the SPBTLE-RF and SPBTLE-1S will function the "same". We are looking at migrating to the SPBTLE-1S to get access to larger xmit packet sizes.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-27 01:21 PM

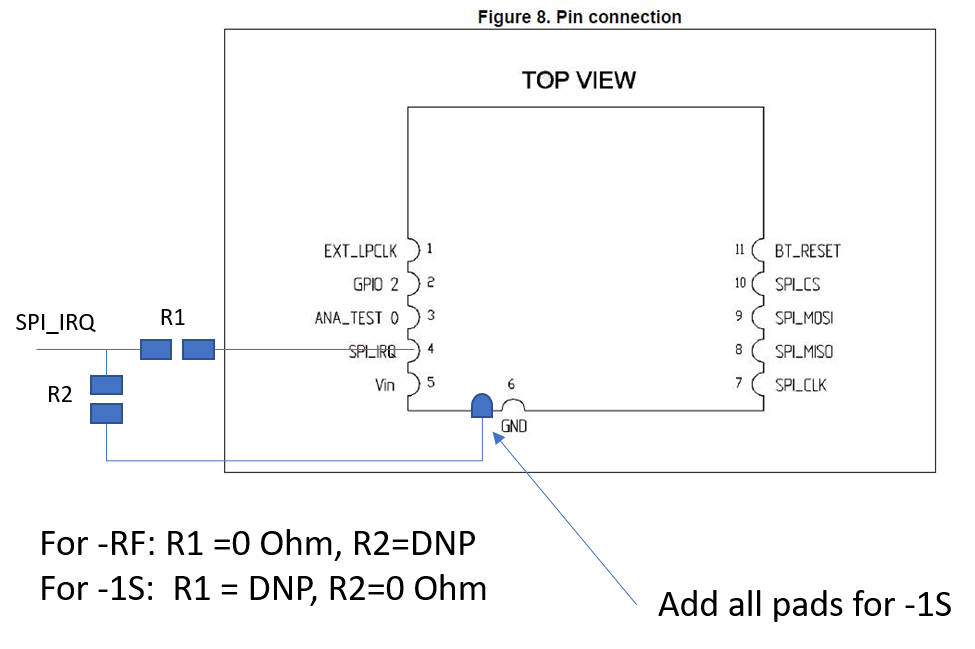

Per your table, it seems like I could make a footprint that would be compatible with either the -1S or the -RF by adding all the pads for the -1S and proving the following jumpers:

Is this correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-28 08:19 AM

I do not believe so. I believe that he is talking about the pinout of the BlueNRG inside the module, not pin 7 of the module itself.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-28 07:03 PM

IO7 would be pin number 7 for SPBTLE-1S module.

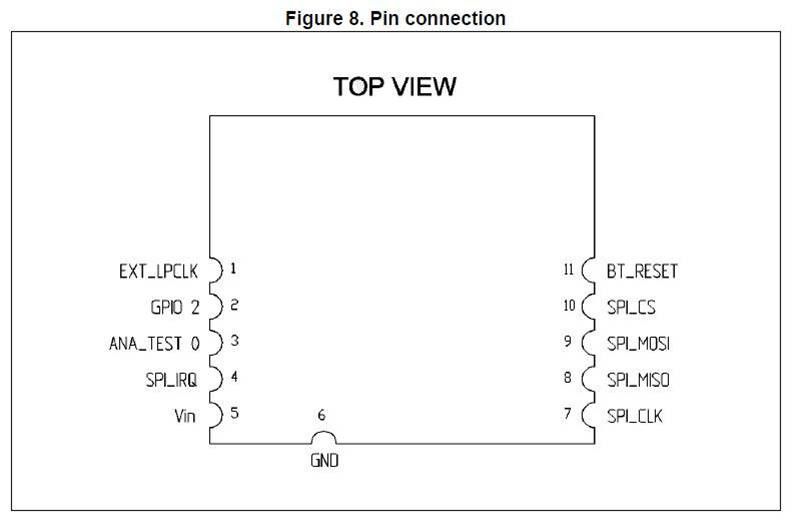

Please refer to DS12065, Table 5:

https://www.st.com/resource/en/datasheet/spbtle-1s.pdf

Download STSW-BLUENRG1-DK:

https://www.st.com/en/embedded-software/stsw-bluenrg1-dk.html