- STMicroelectronics Community

- Product forums

- Interface and connectivity ICs

- Anyone has a driver for QSPI flash S25FL512S?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Anyone has a driver for QSPI flash S25FL512S?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-08 9:36 AM

ST has something on their github but it is incomplete.

The Infineon/Cypress forum offers something here but it is too obtuse.

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-08 11:36 PM

The S25FL512S is in no way special, a driver for e.g. S25FL128S will work, too (as far as reading status reg., read ID are concerned and even for read for the bottom half).

(The changes for 4-byte address mode are rather simple, e.g. change the command bytes accordingly and the ADSIZE field in QUADSPI_CCR, but that's the final step, when read ID etc. work.)

Probably the pin setup is not correct? Check with scope or logic analyzer for activity on NCS, CLK, IO0 and then IO1) and verify that CLK speed is within allowed range for the flash.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-08 10:48 AM

A BSP or an External Loader?

On what STM32, using what pins?

Most BSP should just need to bring up the pins and interface, and get a working READ command in QUAD/32-bit Addressing mode, and then map it.

Got some parts on order from Mouser

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-08 12:47 PM

Hi Clive,

I'm looking for a driver similar to this but for S25FL512S

Don't laugh - this is my first project with a QSPI flash. STM32H753XIH6 custom board.

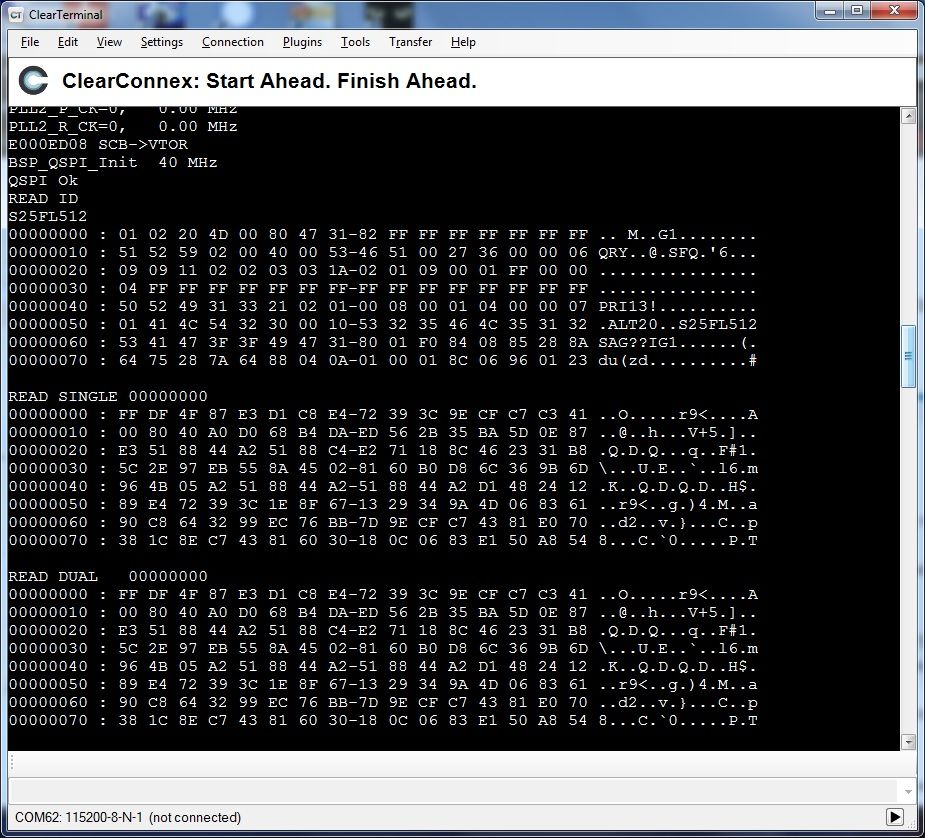

I took the BSP example from STM32H743-EVAL2 for the QSPI itself. Initialization of the QSPI seems successful but then I cannot even read the flash ID or status reg without errors in simple 1-line mode.

The flash is connected with all 4 data pins, on bank1. Bank 2 has a QSPI SDRAM (not enabled yet)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-08 11:36 PM

The S25FL512S is in no way special, a driver for e.g. S25FL128S will work, too (as far as reading status reg., read ID are concerned and even for read for the bottom half).

(The changes for 4-byte address mode are rather simple, e.g. change the command bytes accordingly and the ADSIZE field in QUADSPI_CCR, but that's the final step, when read ID etc. work.)

Probably the pin setup is not correct? Check with scope or logic analyzer for activity on NCS, CLK, IO0 and then IO1) and verify that CLK speed is within allowed range for the flash.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-10 7:22 PM

Thank you @Andreas Bolsch , the S25FL128S driver helped me to tune the QSPI parameters on the READ_ID command and move on.

(By the way, found a bug in the S25FL128S driver, caused probably by recent changes in the "HAL" QSPI driver. Will report it later via github)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-17 1:48 PM

Ok, did get the parts in, and have the read, write, and erase working.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-17 2:55 PM

https://github.com/AVI-crak/Rtos_cortex/tree/master/qspi_driver

I was too lazy to calculate the sector boundaries, keep the data unchanged, and keep track of all this disgrace.

void qspi_data_wire ( uint8_t* data, uint32_t data_size, uint32_t flash_adres);Simple writing of data to an arbitrary address. As long as your memory chip is working, there is no point in checking the status. Well, when it breaks, only a soldering iron will help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-17 3:23 PM

@Community member Have you received S25FL512S or something else?

My board actually has S25FL256S instead of 512 (so it looks from the flash ID info).

The data sheet mentions two variants of S25FL256S: one (which I have) is just a half sized S25FL512S, with same erase block size and all commands.

Another variant has 64KB erase block, more compatible with S25FL128S.

Now when reads/writes/erases basically work, I'm wondering what to do with many protection and options bits marked "OTP".

There are some commands that seem to "freeze" configuration and change of these "OTP" bits. This "freeze" can be done early in bootloader to block user program from doing permanent changes to "OTP" things.

The ECC also looks interesting, I'd like to expose reading the ECC status in my driver.

Their implementation looks more flexible than in the internal flash of STM32h7:

If writing is done in a way not compatible with ECC (several writes into one ECC unit) the ECC in the affected unit just turns off and the write succeeds.

Later user can detect units where ECC was turned off vs. failed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-17 4:06 PM

Yes, the SOIC-16 ones I can fixture. S25FL512SDPMFIG10, 256KB sectors, 4-byte addressing

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-02-17 4:30 PM

That's fantastic ...

- STM32F303RE and X-NUCLEO-IHM07M1 for FOC in STM32 MCUs Products

- CCID USBD transfer block (splitting) in STM32 MCUs Embedded software

- GPDMA in Linked List with OCTOSPI in STM32 MCUs Embedded software

- ST-Link clone drivers in Others: hardware and software

- STM32MP257F-DK: Unable to collect images from MIPI camera in STM32 MPUs Products and hardware related