SPC570s ADC initializing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-11 2:54 AM

Main target is to send an ADC-value to the CAN-BUS.

I took the SPC570xx_RLA CAN Test Application for Discovery

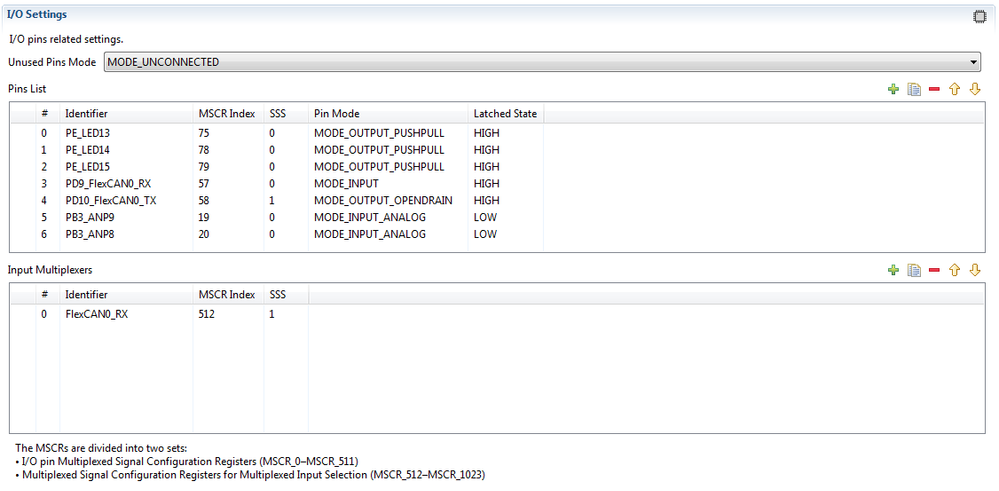

Modified Pin Settings:

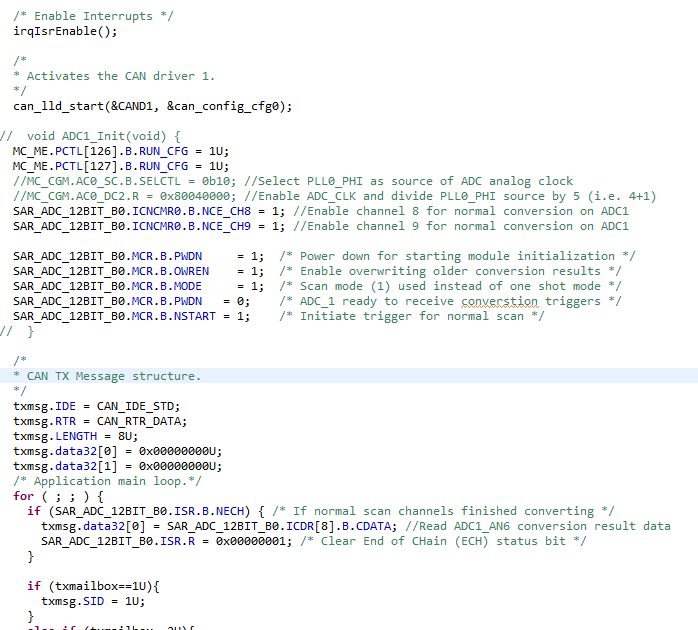

in main.c I tried to initialize and use the ADC:

Without ADC-code CAN example works fine.

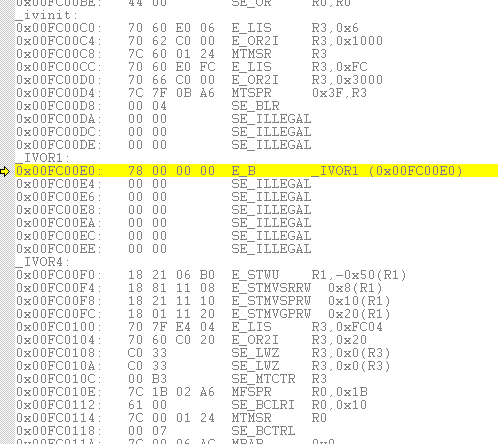

But if I try to get Access to the ADC-regs, System crashes:

The system always stays at the _IVOR1 after SAR_ADC_12BIT_B0.xxxxx = x command.

My hardware is the SPC570S-DISP-Board.

What do I wrong?

#adc #spc570s #spc570s-adcSolved! Go to Solution.

- Labels:

-

ADC

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-11 8:12 AM

Sorry , i was on a bad revision of the reference manual not the last one (Revision 6 RM0349)

Table 12 was not correct on rev 3.

after checking with expert.

here is the answer.

'The problem is not related to wrong address of the supervisor ADC (

SAR_ADC_12BIT_B0

), but It is related to clock gating.

Every time a driver is start (xxx_lld_start) the correct PTCL register is written in order to gate the clock to the peripherals. When using a driver not included in spc5studio

The first operation to do before accessing register is to gate the clock using the function, otherwise IVOR1 is generated.

SPCSetPeripheralClockMode(PCTL NUMBER, (SPC5_ME_PCTL_RUN(2) | SPC5_ME_PCTL_LP(2)));

In this case the PCTL NUMBER for

SAR_ADC_12BIT_B0

is 112 (table 658 in the RM).'

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-11 5:09 AM

Hello Michael ,

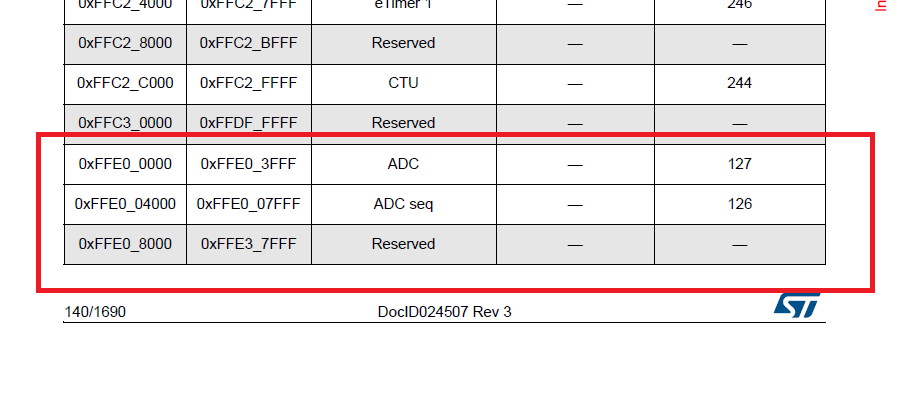

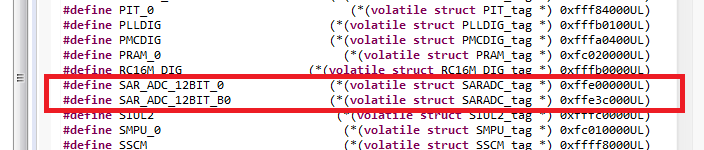

it seems to be a header file issue on SARADC Section & Documentation.

the address 0xFFE3c000 is RESERVED and IVOR1 logical according the RM.

Could you replace SAR_ADC_12BIT_B0 by SAR_ADC_12BIT_0 (cf xpc570s.h)?

Anyway , i am submitting an ER for this inconsistent header file.

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-11 8:12 AM

Sorry , i was on a bad revision of the reference manual not the last one (Revision 6 RM0349)

Table 12 was not correct on rev 3.

after checking with expert.

here is the answer.

'The problem is not related to wrong address of the supervisor ADC (

SAR_ADC_12BIT_B0

), but It is related to clock gating.

Every time a driver is start (xxx_lld_start) the correct PTCL register is written in order to gate the clock to the peripherals. When using a driver not included in spc5studio

The first operation to do before accessing register is to gate the clock using the function, otherwise IVOR1 is generated.

SPCSetPeripheralClockMode(PCTL NUMBER, (SPC5_ME_PCTL_RUN(2) | SPC5_ME_PCTL_LP(2)));

In this case the PCTL NUMBER for

SAR_ADC_12BIT_B0

is 112 (table 658 in the RM).'

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-11 9:24 AM

It works. THX for help.