- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- SPI Master NSS always low in STM32F4

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI Master NSS always low in STM32F4

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 3:34 AM

Hi guys!

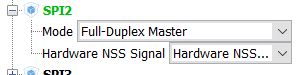

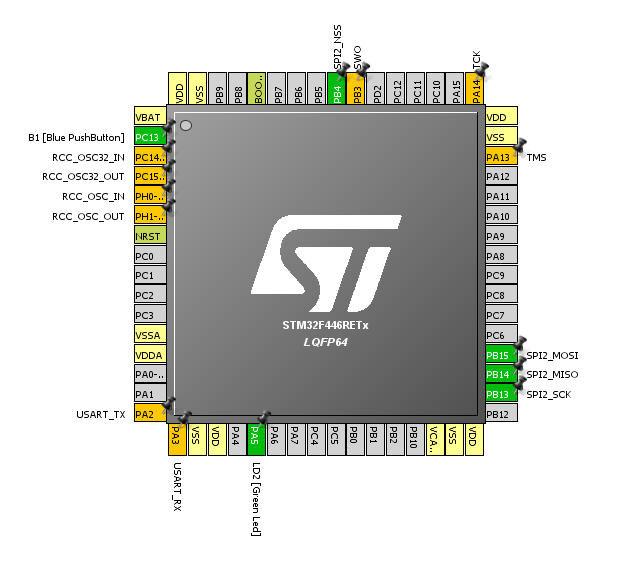

I'm configuring the Nucleo 64 with the STM32F446RE to use SPI as a Master.

The problem I'm having right now is that the NSS pin is always low. Clock and MOSI are perfect. What I would like is that the NSS is high, and goes low during the transmission, then high again.

I've tried setting the NSS as Hardware output, and Software in Cube, but still failed to get what I want.

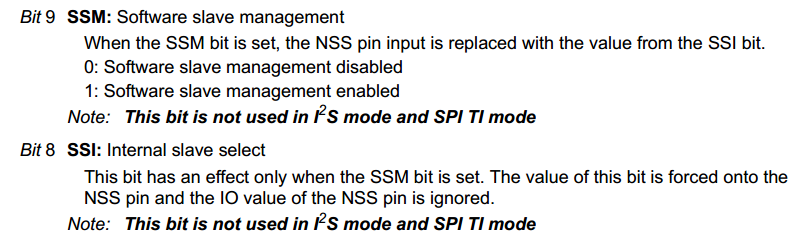

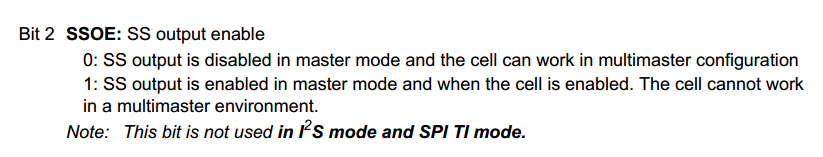

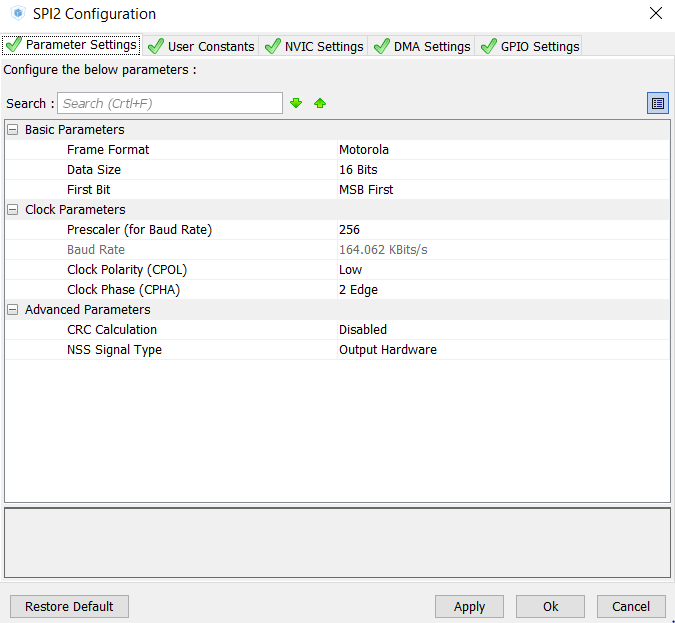

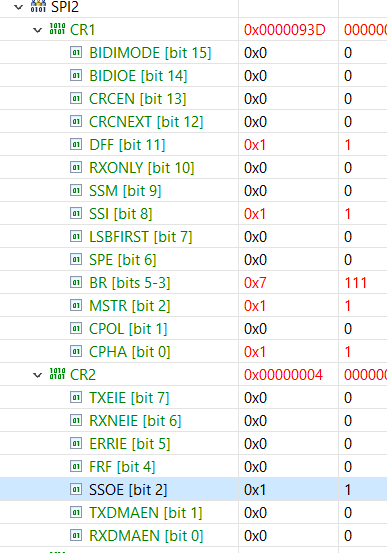

I think this configuration should be sorted with the following 3 bits, from CR1 and CR2. Right now Cube is setting SSOE= 1, SSM=1, SSI=1. And the NSS pin is configured as hardware output in Cube.

Any clues on how should I setup this? I would like to avoid having to use a random pin as CS and pull it manually.

Thanks!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 4:01 AM

If there is only one master SPI, have you tried to make NSS a GPIO (no alternate function)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 4:27 AM

What I would like is that the NSS is high, and goes low during the transmission, then high again.

There's no such functionality in the F4 SPI. In some other STM32 families, NSS may be active only during transmission, but then also toggles between frames (bytes), which may not be what you want either.

You have to do this 'manually', setting the NSS pin as GPIO output. Don't forget the NSS input signal into the SPI module needs to be low (internally) low even if set to soft-NSS.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 5:03 AM

Hi,

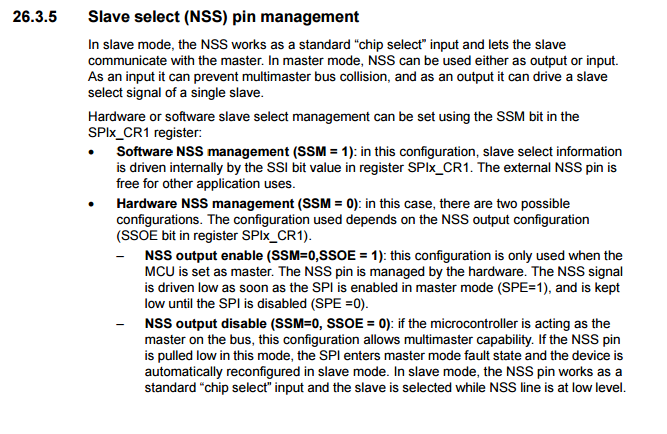

You may assign NSS as GPIO CS, as the reference manual RM0390 says for Hardware NSS management (SSM = 0) that:

NSS output enable (SSM=0,SSOE = 1): this configuration is only used when the MCU is set as master. The NSS pin is managed by the hardware. The NSS signal is driven low as soon as the SPI is enabled in master mode (SPE=1), and is kept low until the SPI is disabled (SPE =0).

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 5:55 AM

There is only one master and one slave. I'm not entirely sure what you mean, to do the Chip Select toggling a pin before and after transmission?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 6:00 AM

Thanks for your help!

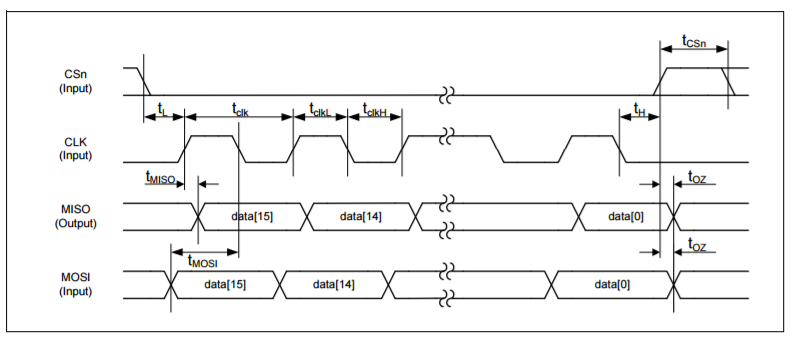

So if I want to implement a simple 16bit spi protocol, as shown (AS5048 encoder), I have to do it manually?

This would negate all advantages of using DMA since I still have to poll the busy flag to set it high again.

What still puzzles me is that the NSS signal goes low immediately after the MX_SPI2_Init() function.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 6:13 AM

Hi Imen, thanks for your answer.

To my understanding, that's what I'm doing in Cube :

And checking the CR1&2 register values after init, it all seems ok, as shown. However, the NSS pin is driven low and stays there.

Any clues?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 6:37 AM

This would negate all advantages of using DMA since I still have to poll the busy flag to set it high again.

Well, not *all* advantages - it still will shovel all the bytes/halfwords you need into the port without processor intervention - but for short frames there's no advantage in it, true.

The SPI implementation in STM32 is, so to speak, underoptimal :)

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 6:45 AM

But most of the SPI slaves need the CS edge to trigger (capture) the internal shift register to memory.. so you need to trigger the CS even though you might be sending 100 bytes.

But I'm still curious, because even though SPE=0, NSS stays low.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-03 7:06 AM

Dear Andres Cao,

Change SSM bit to 1.

On CubeMX, Change NSS signal type to Software output.

Best regards,

Nemui.

- SPI Comminication between two microcontrollers in STM32 MCUs Embedded software

- CCID USBD transfer block on F1 in STM32 MCUs Embedded software

- STM32H753 SPI6 Slave (H7 SPI v2) — Frame qualifies only with NSS-synchronised arming in STM32 MCUs Embedded software

- STM32CUBE RTOS view not working when debugging running target with just symbolFileName supplied to imagesAndSymbols in STM32CubeIDE for Visual Studio Code (MCUs)

- Which Compiler for Safety Application? in STM32 MCUs Embedded software