- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- STM32H7, STM32F7 cache enabled and MPU disabled

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H7, STM32F7 cache enabled and MPU disabled

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-04 4:55 PM

I'm using STM32H723, and STM32F767. CubeMX allows the data cache to be enabed and leave MPU disabled. Is this a valid configuration? Yes, i do know how to configure the MPU. Am i required to enable the MPU and configure all regions to have same attributes if i simply want the whole SRAM to be cacheable?

Solved! Go to Solution.

- Labels:

-

STM32CubeMX

-

STM32F7 series

-

STM32H7 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-04 5:50 PM

> CubeMX allows the data cache to be enabed and leave MPU disabled. Is this a valid configuration?

Yes.

> Am i required to enable the MPU and configure all regions to have same attributes if i simply want the whole SRAM to be cacheable?

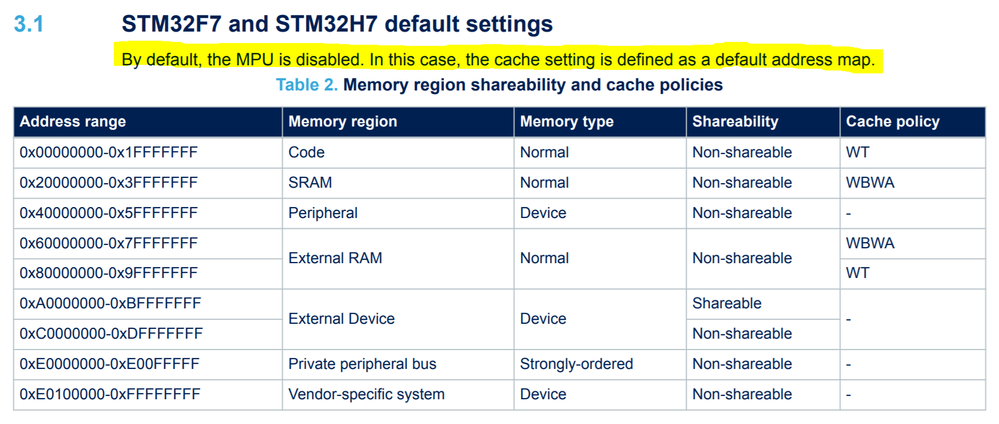

No. SRAM is write-back write-allocate cached by default (at least on the H7). You can use the MPU to override this, but don't have to.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-04 5:50 PM

> CubeMX allows the data cache to be enabed and leave MPU disabled. Is this a valid configuration?

Yes.

> Am i required to enable the MPU and configure all regions to have same attributes if i simply want the whole SRAM to be cacheable?

No. SRAM is write-back write-allocate cached by default (at least on the H7). You can use the MPU to override this, but don't have to.

- HRTIM1, TIMA output2 configuration issue in STM32CubeMX (MCUs)

- Is there a way in MX2 to enable/disable timer freezing during debugging? in STM32CubeMX2 (MCUs)

- STM32H745XI6 – Unable to read device ID from ROM table after disabling BCM7 (boot CM4 only) in STM32CubeProgrammer (MCUs)

- RTOS proxy does not properly start when trying to debug with hot-attachement in STM32CubeIDE for Visual Studio Code (MCUs)

- STM32N6570-DK - debugger loses connection in STM32CubeIDE (MCUs)