- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs Embedded software and solutions

- Re: Stm32mp157 Ethernet problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Stm32mp157 Ethernet problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-28 5:31 AM

An urgent problem occurred in stm32mp157. I used ksz9031 network chip, but it could not be used. The LOG is as follows,

[ 18.996823] Micrel KSZ9031 Gigabit PHY stmmac-0:00: attached PHY driver [Micrel KSZ9031 Gigabit PHY] (mii_bus:phy_addr=stmmac-0:00, irq=POLL)

Starting Wait for Network to be Configured...

[ 19.122107] stm32-dwmac 5800a000.ethernet: Failed to reset the dma

[ 19.127072] stm32-dwmac 5800a000.ethernet eth0: stmmac_hw_setup: DMA engine initialization failed

[ 19.135979] stm32-dwmac 5800a000.ethernet eth0: stmmac_open: Hw setup failed

I can't solve this problem

Solved! Go to Solution.

- Labels:

-

Ethernet

-

STM32MP15 Lines

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-05 9:06 AM

Hi,

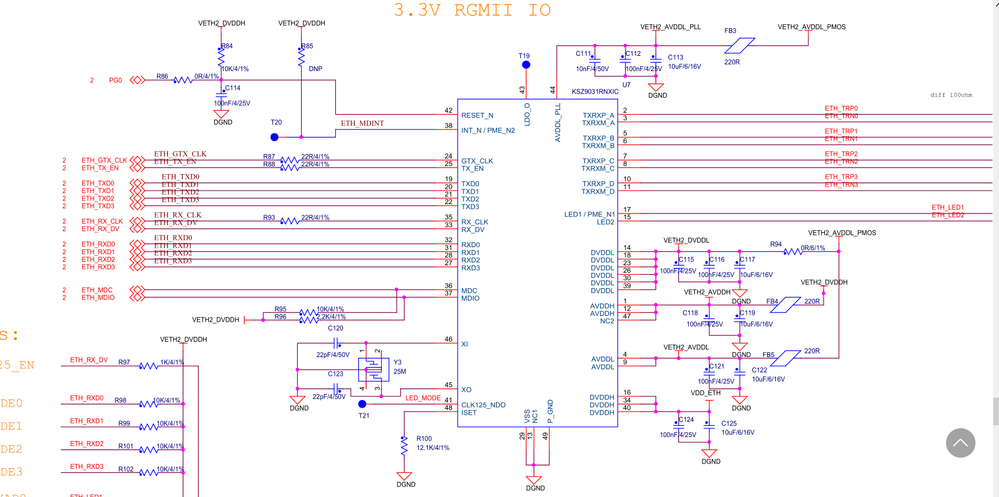

the pin 41 of KSZ9031 should provide the 125 MHz clock to STM32MP1 (and this is the simpler and preferred solution), but in your schematic it is instead connected only to a test point.

If you cannot rework your board, you need to provide the 125 MHz internally in STM32MP1.

Check the STM32MP1 Reference Manual at chapter 10.4.8 "clock distribution for Ethernet (ETH)".

The input named "ETH_CLK125" is the one missing in your board, so has to be replaced with a 125 MHz clock arriving from pll4_p_ck or pll3_q_ck. Now we need to set all the internal switches to achieve this.

Use also the document Documentation/devicetree/bindings/net/stm32-dwmac.txt for reference.

1) mux between ETH_CLK125 and eth_clk_fb: change its position adding DT property:

st,eth_clk_sel = <1>;2) enable the gate controlled by ETHCKEN: for this you need to add two more clocks in the DT:

To clock-names add "eth-ck" and "syscfg-clk"

To clocks add ETHCK_K and SYSCFG

The point 1) and 2) can be put in your board DT as:

ðernet0 {

status = "okay";

st,eth_clk_sel = <1>;

clock-names = "stmmaceth",

"mac-clk-tx",

"mac-clk-rx",

"eth-ck",

"syscfg-clk",

"ethstp";

clocks = <&rcc ETHMAC>,

<&rcc ETHTX>,

<&rcc ETHRX>,

<&rcc ETHCK_K>,

<&rcc SYSCFG>,

<&rcc ETHSTP>;

};Now it remains the mux between pll4_p_ck or pll3_q_ck and the frequency from the PLL. This has to be done in the DT of tf-a (if you use secure boot) or DT of U-Boot (if you use the basic boot). The DT is the same in the two cases, just stored in a different file:

- tf-a has DT in folder ./fdts/

- u-boot has DT in folder ./arch/arm/dts/

At linux boot, this command gives you the dump of the clock tree. You need to verify there if the clock frequency is correct

cat /sys/kernel/debug/clk/clk_summaryYou also need to set a frequency that is suitable for all the users of the same PLL

Let's go to edit the DT!

4) mux source: replace CLK_ETH_DISABLED with CLK_ETH_PLL4P or with CLK_ETH_PLL3Q

in my test I used pll4_p

5) change the numbers in node "pll3: st,pll@2" or "pll4: st,pll@3"

one possible settings for pll4_p at 125 MHz (suppose crystal on HSE is 24 MHz) is

/* VCO = 750.0 MHz, P=125, Q=62.5, R=62.5 */

pll4: st,pll@3 {

cfg = <3 124 5 11 11 PQR(1,1,1)>;

};- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-29 12:38 AM

See https://wiki.st.com/stm32mpu/wiki/Ethernet_overview#How_to_debug

This error is usually linked to a clock not active on the ETH IP boundary when the reset is requested (see RM0436, look at RCC section "Clock distribution for Ethernet (ETH)"). E.g. check if clocks are present on ETH_CLK125 and ETH_RX_CLK pins.

Is your PHY set-up in similar way that the one on EV1 (MB1262) or DK2 (MB1272) boards ? You could also see AN5031.

Check also if you PHY is powered at the time of the ETH reset.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-29 1:47 AM

- This is my ksz9031 circuit diagram

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-29 2:53 AM

CLK125_NDO (125MHz clock from PHY) should normally be connected to ETH_CLK125 pin (PG5).

if you omit that intentionally, you need to feed internally the ETH with a precise 125MHz clock from RCC pll3_q or pll4_p (this might constrain your clock tree choices) and do the relevant settings in the DeviceTree (see https://wiki.st.com/stm32mpu/wiki/Ethernet_device_tree_configuration)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-29 3:04 AM

- Can you simply provide Settings for these two clocks on the device tree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-29 11:11 PM

- Can you provide more description of configuring device tree clock

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-05 9:06 AM

Hi,

the pin 41 of KSZ9031 should provide the 125 MHz clock to STM32MP1 (and this is the simpler and preferred solution), but in your schematic it is instead connected only to a test point.

If you cannot rework your board, you need to provide the 125 MHz internally in STM32MP1.

Check the STM32MP1 Reference Manual at chapter 10.4.8 "clock distribution for Ethernet (ETH)".

The input named "ETH_CLK125" is the one missing in your board, so has to be replaced with a 125 MHz clock arriving from pll4_p_ck or pll3_q_ck. Now we need to set all the internal switches to achieve this.

Use also the document Documentation/devicetree/bindings/net/stm32-dwmac.txt for reference.

1) mux between ETH_CLK125 and eth_clk_fb: change its position adding DT property:

st,eth_clk_sel = <1>;2) enable the gate controlled by ETHCKEN: for this you need to add two more clocks in the DT:

To clock-names add "eth-ck" and "syscfg-clk"

To clocks add ETHCK_K and SYSCFG

The point 1) and 2) can be put in your board DT as:

ðernet0 {

status = "okay";

st,eth_clk_sel = <1>;

clock-names = "stmmaceth",

"mac-clk-tx",

"mac-clk-rx",

"eth-ck",

"syscfg-clk",

"ethstp";

clocks = <&rcc ETHMAC>,

<&rcc ETHTX>,

<&rcc ETHRX>,

<&rcc ETHCK_K>,

<&rcc SYSCFG>,

<&rcc ETHSTP>;

};Now it remains the mux between pll4_p_ck or pll3_q_ck and the frequency from the PLL. This has to be done in the DT of tf-a (if you use secure boot) or DT of U-Boot (if you use the basic boot). The DT is the same in the two cases, just stored in a different file:

- tf-a has DT in folder ./fdts/

- u-boot has DT in folder ./arch/arm/dts/

At linux boot, this command gives you the dump of the clock tree. You need to verify there if the clock frequency is correct

cat /sys/kernel/debug/clk/clk_summaryYou also need to set a frequency that is suitable for all the users of the same PLL

Let's go to edit the DT!

4) mux source: replace CLK_ETH_DISABLED with CLK_ETH_PLL4P or with CLK_ETH_PLL3Q

in my test I used pll4_p

5) change the numbers in node "pll3: st,pll@2" or "pll4: st,pll@3"

one possible settings for pll4_p at 125 MHz (suppose crystal on HSE is 24 MHz) is

/* VCO = 750.0 MHz, P=125, Q=62.5, R=62.5 */

pll4: st,pll@3 {

cfg = <3 124 5 11 11 PQR(1,1,1)>;

};- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-02-19 6:47 AM

For anyone trying to solve this problem today, please note there is a crucial typo in Antonio's answer.

This is incorrect:

st,eth_clk_sel = <1>;Using that will cause your clocks to not enable. You must use the following declaration:

st,eth-clk-sel = <1>;This was found after hours of testing and then reviewing the source code to determine how to enable the PPL4P clocks, which were stuck in a disabled mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-07 10:29 AM

Does this solution require any updates considering it is many years later? I have the same situation now where there is no CLK_125 input but it doesn't help. I have PLL4P at 125mhz and added everything mentioned including the below fix for

st,eth_clk_sel = <1>;

- OpenSTLinux on MYiR MYD-LD25X development board and 8th programming language in STM32 MPUs Products

- STM32MP15 ECO 5.0 Touch display - Weston calibrator, x inverson and save/restore calibration data in STM32 MPUs Products

- Interfacing Touchscreen (edt-ft5406) with stm32mp157c in Linux-Kernel in STM32 MPUs Products

- Enable Counter Driver on zephyr in STM32 MPUs Embedded software and solutions

- STM32MP1: Flicker-free Bootscreen / Splashscreen during startup in STM32 MPUs Embedded software and solutions