- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs Boards and hardware tools

- Horrible signal reflections and timing violations ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Horrible signal reflections and timing violations in DDR3L HyperLynx simulation of the STM32MP157 Discovery

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-29 09:07 AM

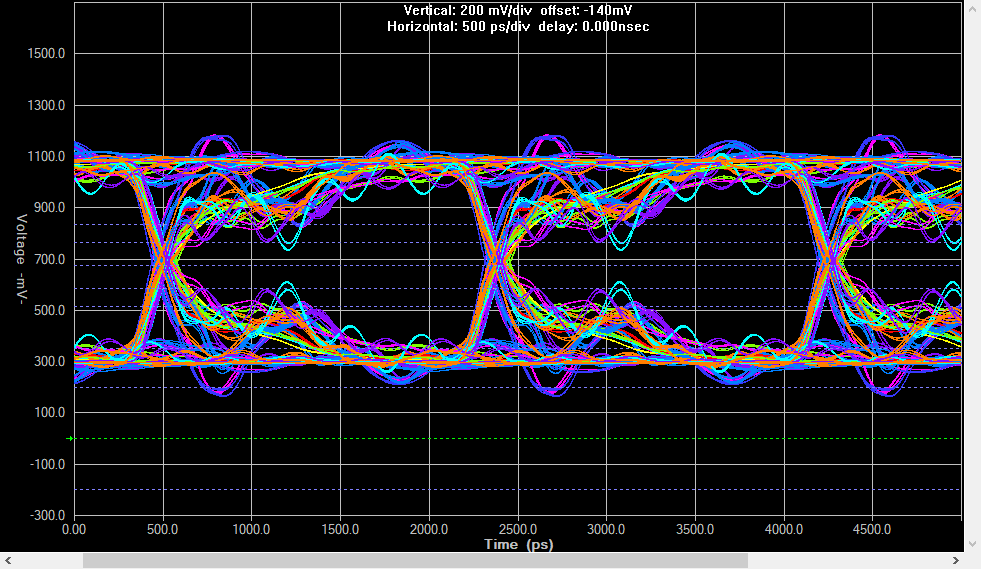

I'm running the STM32MP157A-DK Discovery board through HyperLynx and I'm getting some pretty horrible ringing on the address lines, along with timing violations when I use the DDRx Batch Simulation, and I'd like to verify my setup is good.

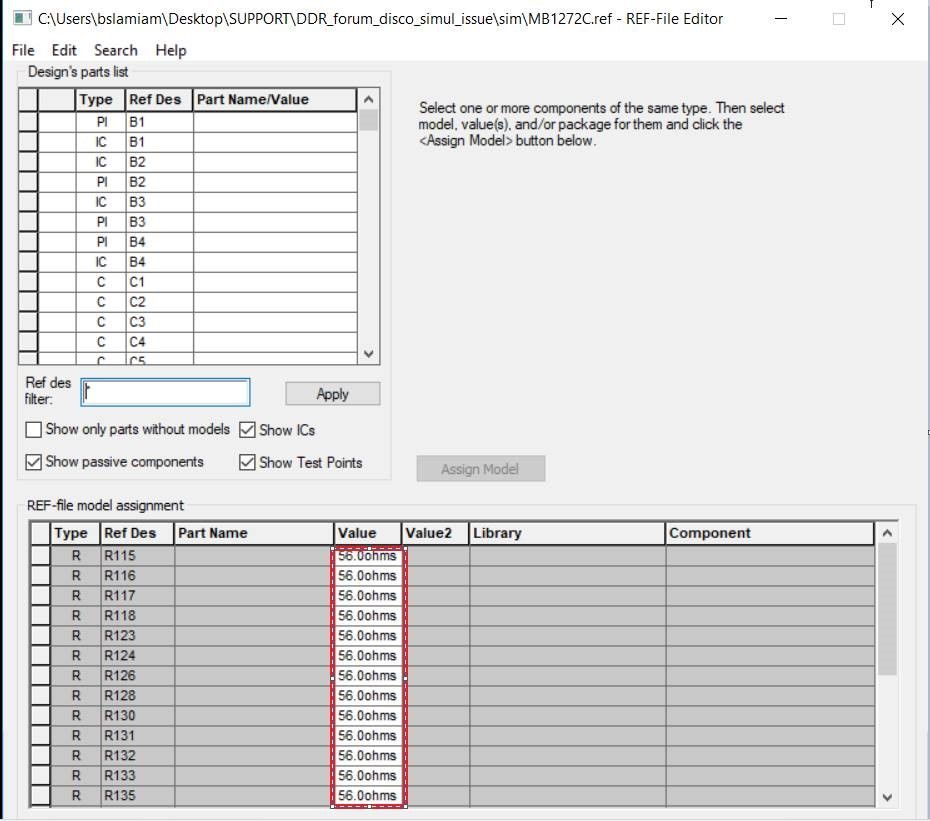

First, I exported the board from Altium using the HyperLynx exporter, and then opened it up in HyperLynx, added my IBIS models, set my pins to MSD_D3RP3L_48, set all the address / command termination resistors to 56 ohms as indicated in the schematic, and ran an eye diagram, as seen at the memory chip die:

There's substantial ringing on the bus, which appears to be caused by the long stubs that run off to termination resistors.

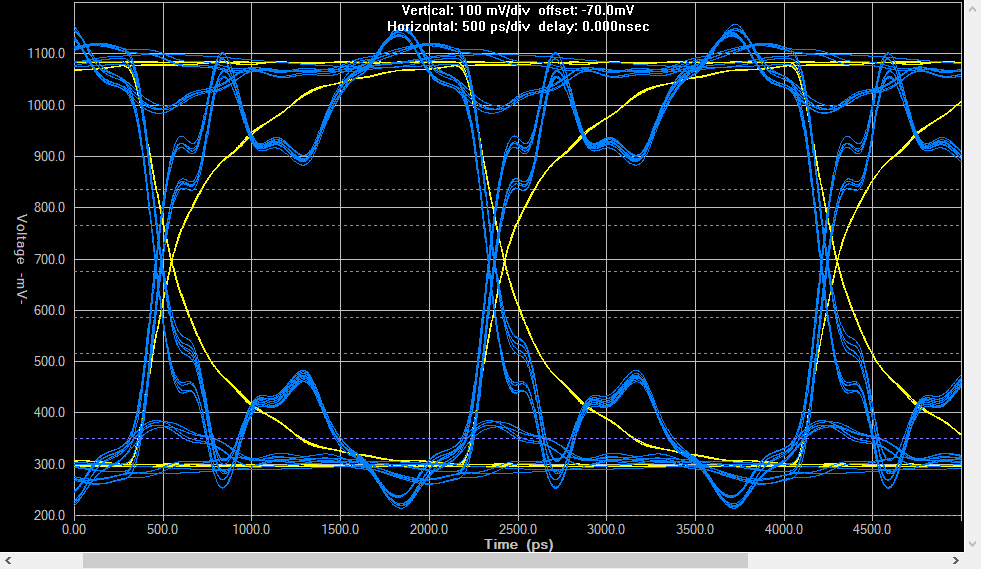

To check that theory out, let's focus on the yellow DDR_A7 signal (one of the shortest stubs on the PCB), and DDR_A12 in blue (one of the longest):

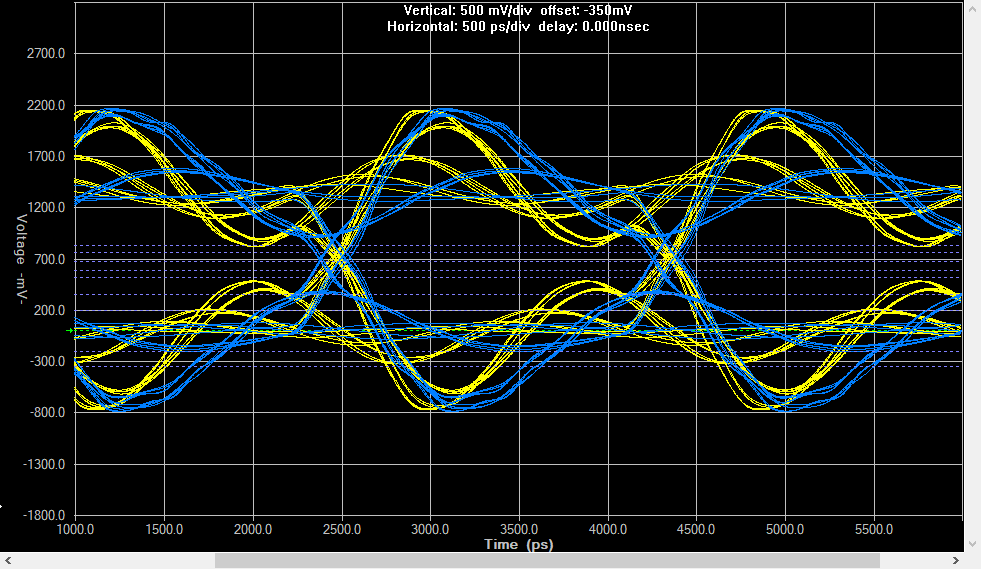

Clearly, the stubs off to the VTT resistors appear to be causing the problem, as the longer-stub signal is much worse. I reran the simulation with very very large values of resistors, just to ensure that my simulation was correctly using the 56-ohm resistors (if they were DNI'd, the unterminated stubs would definitely cause issues). I got way worse data, as expected:

So, my first question is whether the above results are consistent with other people's simulations of the design? Is there something I'm missing?

Next, I ran the DDRx Batch Simulation. HyperLynx flagged every pin with some sort of read operation setup time margin failure.

I've attached my simulation project with the DDRx Batch Simulation results.

Is there something I'm doing wrong? I'd appreciate any insight! Thanks!

- Labels:

-

ST-Boards

-

STM32MP15 Lines

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-09 04:34 AM

Hi @Community member

Sorry for late feedback.

This is some comments from our expert :

1 - You should define ground plane in stackup

2 - Add following lines in wildcat ibis model ( precise differential pairs)

|**********************DIFF PIN*********************************************

[Diff_pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

|

N22 N23 0.320V 0ns NA NA |CK

G22 G23 0.320V 0ns NA NA |DQS0

U22 U23 0.320V 0ns NA NA |DQS1

C22 B23 0.350V 0ns NA NA |DQS2

AB22 AB23 0.350V 0ns NA NA |DQS3

3 - precise termination resistance values

Hope it help

BR,

Olivier

In order to give better visibility on the answered topics, please click on 'Accept as Solution' on the reply which solved your issue or answered your question.