- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs TouchGFX and GUI

- Problems with CubeMX + STM32CubeIDE + touchGFX

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problems with CubeMX + STM32CubeIDE + touchGFX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-10 1:31 AM

Question 1:

We are developing a custom board based on STM32H750B-DK.

We have a “custom touch�? on it, so I have to adapt the “component�? to CubeMX-TouchGFX structure.

The question: in the STM32H750B-DK project template we find files stm32h750b_discovery_ts.h / .c

This component will be initialized by TouchGFX part, using BSP_TS_Init.

This will call MX_I2C4_Init(); but this is also already called by main.c generated from CubeMX itself…

How should I procced to make a “clean�? implementation? I should not activate I2C4 on CubeMX, so that it is not generated?

Question 2:

We have a project for our board where we can modify CubeMX and TouchGFX part, and regenerate it, keeping our own written code.

This was OK until I worked with TouchGFX 4.15.0. After I upgraded it to 4.16.0, I have problems, loosing my cone in TouchGFX part, and nothing more comes on display

Also I needed to correct by hand static TouchGFXHAL hal(dma, display, tc, 480, 800);

(it was generated as static TouchGFXHAL hal(dma, display, tc, , 32);

Are there know issues in this migration 4.15.0 -> 4.16.0 I should consider or did I something wrong?

Question 3:

Our board has a bigger Display then demo-kit.

setFrameBufferStartAddresses((void*)0xD0000000, (void*)0xD003FC00, (void*)0); (demokit: W=480; H=272)

How should I calculate the starting point of the second buffer? W*H*depth is enough? (480=w*800=H*4) or should I consider also additional bytes?

Question 4:

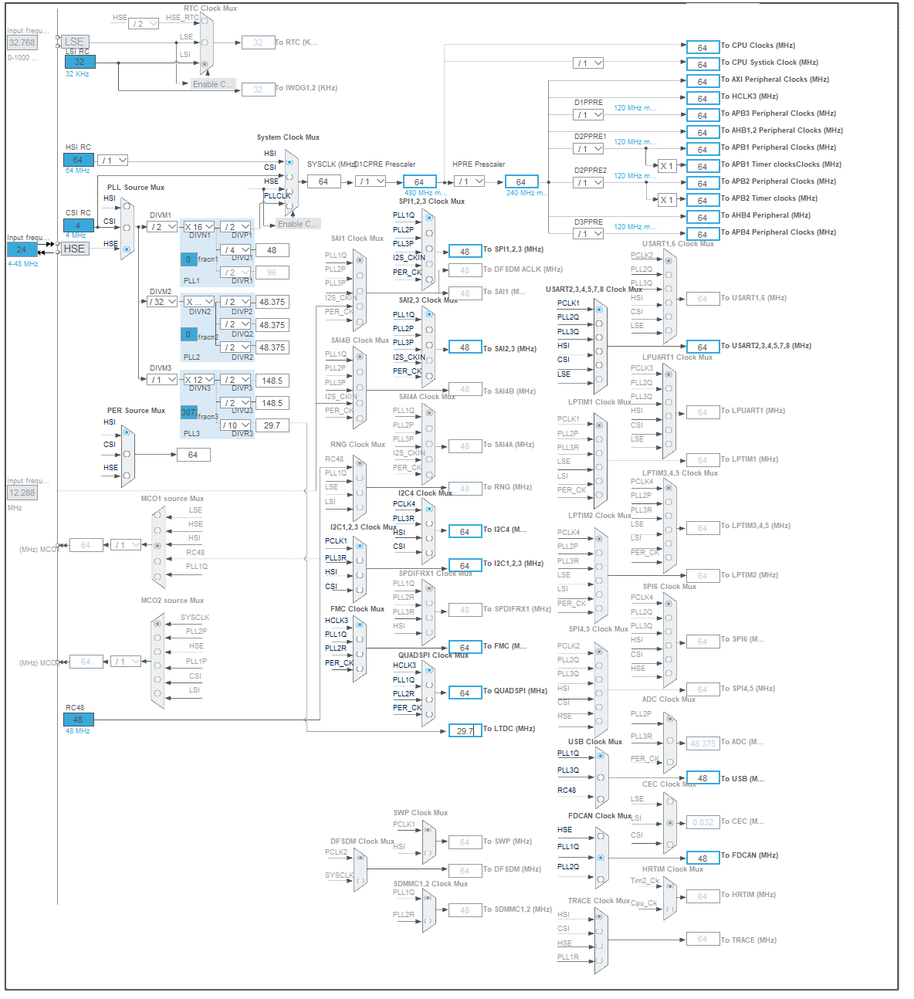

I have problems with CubeMX, to generate the correct timing. I have a working timing configuration set, done “by hand�?.

I would like to be able to generate it from CubeMX, so I can still continue use it to update the generated part of the project,

But I’m not able to set clock-timing, that generates a working set of settings.

I tried to identify which parameters I should modify, to receive the desired set of settings, but was not able to make this kind of “reverse work�?

Can you help me?

void Manual_SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

RCC_PeriphCLKInitTypeDef PeriphClkInitStruct = {0};

/** Supply configuration update enable

*/

HAL_PWREx_ConfigSupply(PWR_LDO_SUPPLY);

/** Configure the main internal regulator output voltage

*/

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE1);

while (!__HAL_PWR_GET_FLAG(PWR_FLAG_VOSRDY)) {

}

/** Macro to configure the PLL clock source

*/

__HAL_RCC_PLL_PLLSOURCE_CONFIG(RCC_PLLSOURCE_HSE);

/** Initializes the CPU, AHB and APB busses clocks

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSI48 | RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_BYPASS;

RCC_OscInitStruct.HSI48State = RCC_HSI48_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 5;

RCC_OscInitStruct.PLL.PLLN = 160;

RCC_OscInitStruct.PLL.PLLP = 2;

RCC_OscInitStruct.PLL.PLLQ = 4;

RCC_OscInitStruct.PLL.PLLR = 2;

RCC_OscInitStruct.PLL.PLLRGE = RCC_PLL1VCIRANGE_2;

RCC_OscInitStruct.PLL.PLLVCOSEL = RCC_PLL1VCOWIDE;

RCC_OscInitStruct.PLL.PLLFRACN = 0;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK) {

Error_Handler();

}

/** Initializes the CPU, AHB and APB busses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

| RCC_CLOCKTYPE_PCLK1 | RCC_CLOCKTYPE_PCLK2 | RCC_CLOCKTYPE_D3PCLK1

| RCC_CLOCKTYPE_D1PCLK1;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.SYSCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV2;

RCC_ClkInitStruct.APB3CLKDivider = RCC_APB3_DIV2;

RCC_ClkInitStruct.APB1CLKDivider = RCC_APB1_DIV2;

RCC_ClkInitStruct.APB2CLKDivider = RCC_APB2_DIV2;

RCC_ClkInitStruct.APB4CLKDivider = RCC_APB4_DIV2;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2) != HAL_OK) {

Error_Handler();

}

PeriphClkInitStruct.PeriphClockSelection = RCC_PERIPHCLK_LTDC

| RCC_PERIPHCLK_USART3 | RCC_PERIPHCLK_USART2 | RCC_PERIPHCLK_UART4

| RCC_PERIPHCLK_FDCAN | RCC_PERIPHCLK_UART5 | RCC_PERIPHCLK_SPI1

| RCC_PERIPHCLK_SAI2 | RCC_PERIPHCLK_I2C1 | RCC_PERIPHCLK_I2C4

| RCC_PERIPHCLK_USB | RCC_PERIPHCLK_QSPI | RCC_PERIPHCLK_FMC;

PeriphClkInitStruct.PLL3.PLL3M = 5;

PeriphClkInitStruct.PLL3.PLL3N = 160;

PeriphClkInitStruct.PLL3.PLL3P = 2;

PeriphClkInitStruct.PLL3.PLL3Q = 2;

PeriphClkInitStruct.PLL3.PLL3R = 83;

PeriphClkInitStruct.PLL3.PLL3RGE = RCC_PLL3VCIRANGE_2;

PeriphClkInitStruct.PLL3.PLL3VCOSEL = RCC_PLL3VCOWIDE;

PeriphClkInitStruct.PLL3.PLL3FRACN = 0;

PeriphClkInitStruct.FmcClockSelection = RCC_FMCCLKSOURCE_D1HCLK;

PeriphClkInitStruct.QspiClockSelection = RCC_QSPICLKSOURCE_D1HCLK;

PeriphClkInitStruct.Sai23ClockSelection = RCC_SAI23CLKSOURCE_PLL;

PeriphClkInitStruct.Spi123ClockSelection = RCC_SPI123CLKSOURCE_PLL;

PeriphClkInitStruct.FdcanClockSelection = RCC_FDCANCLKSOURCE_PLL;

PeriphClkInitStruct.Usart234578ClockSelection =

RCC_USART234578CLKSOURCE_D2PCLK1;

PeriphClkInitStruct.I2c123ClockSelection = RCC_I2C123CLKSOURCE_D2PCLK1;

PeriphClkInitStruct.UsbClockSelection = RCC_USBCLKSOURCE_HSI48;

PeriphClkInitStruct.I2c4ClockSelection = RCC_I2C4CLKSOURCE_D3PCLK1;

if (HAL_RCCEx_PeriphCLKConfig(&PeriphClkInitStruct) != HAL_OK) {

Error_Handler();

}

/*## LTDC Clock Configuration ###########################################*/

RCC_PeriphCLKInitTypeDef periph_clk_init_struct;

/* DISPLAY_ILITEK LCD clock configuration */

/* LCD clock configuration */

/* PLL3_VCO Input = HSE_VALUE/PLL3M = 5 Mhz */

/* PLL3_VCO Output = PLL3_VCO Input * PLL3N = 800 Mhz */

/* PLLLCDCLK = PLL3_VCO Output/PLL3R = 800/83 = 9.63 Mhz */

/* PLLLCDCLK = PLL3_VCO Output/PLL3R = 800/15 = 53 Mhz */

/* LTDC clock frequency = PLLLCDCLK = 9.63 Mhz */

periph_clk_init_struct.PeriphClockSelection = RCC_PERIPHCLK_LTDC;

periph_clk_init_struct.PLL3.PLL3M = 5;

periph_clk_init_struct.PLL3.PLL3N = 160;

periph_clk_init_struct.PLL3.PLL3FRACN = 0;

periph_clk_init_struct.PLL3.PLL3P = 2;

periph_clk_init_struct.PLL3.PLL3Q = 2;

periph_clk_init_struct.PLL3.PLL3R = 27; // 30 MHz: 800/27 = 29.6 MHz

// periph_clk_init_struct.PLL3.PLL3R = 20; // 40 MHz: 800/20 = 40.0 MHz

// periph_clk_init_struct.PLL3.PLL3R = 32; // 25 MHz: 800/32 = 25.0 MHz

// periph_clk_init_struct.PLL3.PLL3R = 13; // 60 MHz: 800/13 = 61.5 MHz

// periph_clk_init_struct.PLL3.PLL3R = 12; // 65 MHz: 800/12 = 66.7 MHz

// periph_clk_init_struct.PLL3.PLL3R = 16; // 50 MHz: 800/16 = 50.0 MHz

// periph_clk_init_struct.PLL3.PLL3R = 15; // 55 MHz: 800/16 = 53.3 MHz

// periph_clk_init_struct.PLL3.PLL3R = 17; // 45 MHz: 800/17 = 47.1 MHz

// periph_clk_init_struct.PLL3.PLL3R = 18; // 45 MHz: 800/18 = 44.4 MHz

HAL_RCCEx_PeriphCLKConfig(&periph_clk_init_struct);

/** Enable USB Voltage detector

*/

HAL_PWREx_EnableUSBVoltageDetector();

}

- Labels:

-

STM32CubeIDE

-

STM32CubeMX

-

TouchGFX

- SM32N6570-DK Camera Guide in STM32 MCUs Embedded software

- STM32H745I-DISCO – External flash erase/init failure with TouchGFX project in STM32 MCUs Embedded software

- TouchGFX Button with Label Text position problem in STM32 MCUs TouchGFX and GUI

- Failing to make display show anything on the STM32H757I-EVAL board in STM32 MCUs Embedded software

- Unable to debug a TouchGFX example project in STM32CubeIDE in STM32 MCUs TouchGFX and GUI