Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs TouchGFX and GUI

- Problem with lvgl, LTDC, DMA2D, SDRAM

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problem with lvgl, LTDC, DMA2D, SDRAM

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-10-27 6:04 AM

I have custom board with 800x480 TFT display, external SDRAM and STM32H745II MCU.

I have two problems that can be related, but I'm not sure

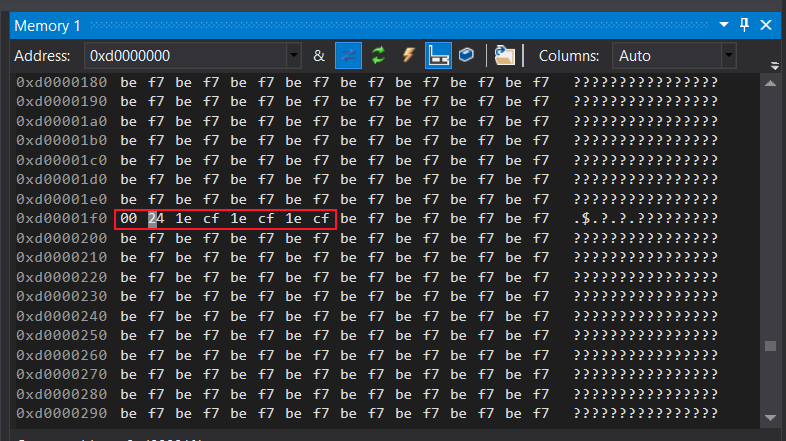

- When I'm trying to change one byte in the SDRAM from the debugger Memory window, 8 bytes around it change, mostly to zero, sometimes to some random values. It works in IAR IDE and in VisualGDB (OpenODC + GDB). If I try to change one byte from the firmware, everything works good.

- I'm porting lvgl to my board. Video memory is located in the external SDRAM. I try to use DMA2D to write internal lvgl buffer to the video memory (implementing flush_cb lvgl function). Sometimes, depending on the widget coordinates and size, calculated DMA2D addresses and offsets become not aligned by 8 bytes. In this case after the transfer I see from 1 to 3 zero pixels on the image, at the end of the each copied image line. In the memory there are 2 to 6 zero bytes, from the end of the image line to the next 8-byte alligned address.

Is it some SDRAM\FMC specific, or DMA2D aligment requirement? Or can it be misconfiguration in FMC, LTDC or DMA2D? Memory cache problem?

Picture 1: 5 lvgl progress bars, drawn with 1 pixel step in the x coordinate. You can see black 1-3 pixel width black borders.

Picture 2: Memory state after I tried to change 1 byte at 0xd00001f0. All 8 bytes are reseted to some values.

Labels:

- Labels:

-

DMA2D

-

FMC-FSMC

-

LCD-LTDC

-

STM32H7 series

This discussion is locked. Please start a new topic to ask your question.

0 REPLIES 0

Related Content

- Unexpected data corruption when camera and display both running (with SDRAM framebuffers in between) in STM32 MCUs Products

- External QSPI NOR flash read and write operation in STM32 MCUs Embedded software

- Failing to make display show anything on the STM32H757I-EVAL board in STM32 MCUs Embedded software

- DMA2D Transfer Complete (TCIF=1) but destination AXI SRAM is always 0 in STM32 MCUs Embedded software

- STM32H750B-DK: Integrate LwIP Ethernet + TouchGFX + External QSPI Flash in STM32 MCUs TouchGFX and GUI