TIM1 timer, register TIM1_BDTR, bit OSSI. What is the function?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-06 12:28 PM

A citation from 'RM0041. Reference manual. STM32F100xx':

OSSI: Off-state selection for Idle mode

This bit is used when MOE=0 on channels configured as outputs....0: When inactive, OC/OCN outputs are disabled (OC/OCN enable output signal=0).1: When inactive, OC/OCN outputs are forced first with their idle level as soon as CCxE=1 orCCxNE=1 (OC/OCN enable output signal=1).But. My experiments on

STM32F100RB have shown that this bit has no effect on the state of the outputs.

Can someone have an example of using the OSSI bit?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-07 4:37 PM

Hello!

Go to

and download the firmware.Inside , you can find an example using the Break Feature (and OSSI bit)

Regards

VF

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-07 11:16 PM

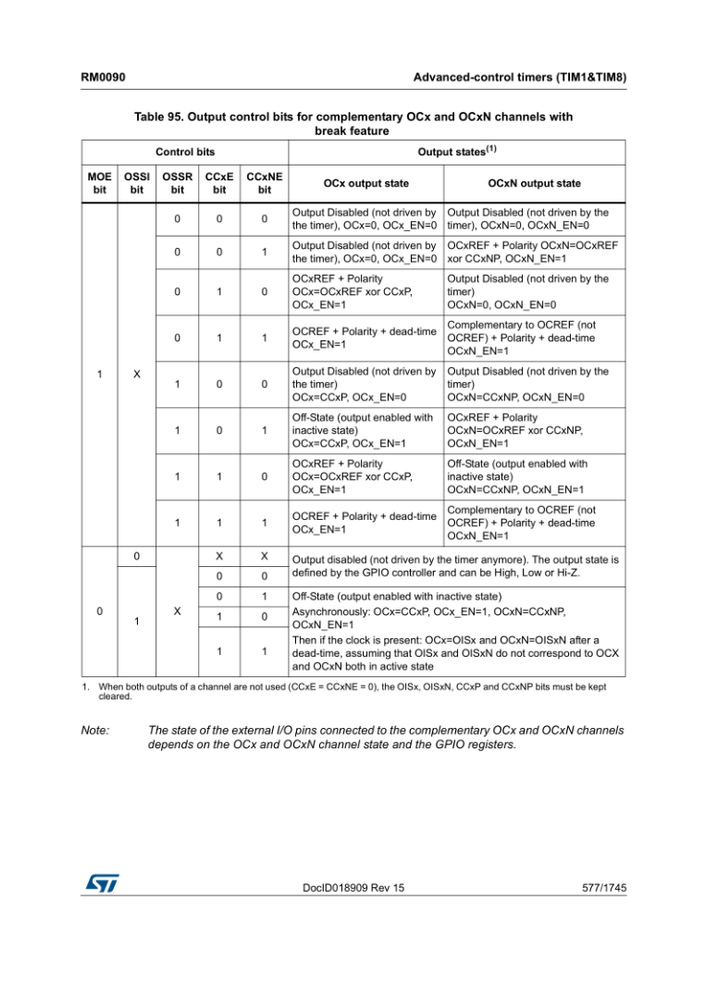

This table is in RM0090 for the 'F4 and its second part (MOE=0) sheds some light on the OSSI issue:

In other words, if MOE=0 (which is the consequence of break input getting active, i.e. the ''something terrible happened, bail out'' mechanism engaged) you can chose if the outputs go threestate (when OSSI=0), or driven to a given state (see narrative there).

It appears that this table is incomplete in RM0041 - would like to know if on purpose or by mistake.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-08 12:53 PM

Thank you all for helping me to solve my problem.

Vangelis Fortounas, in that example bit OSSI is set to 1:

...

sBreakConfig.OffStateIDLEMode = TIM_OSSI_ENABLE; ... HAL_TIMEx_ConfigBreakDeadTime(&TimHandle, &sBreakConfig); ...I would like to know the difference between the two modes (OSSI=0 and OSSI=1).

waclawek.jan, in my case, i could not get 'disabled state' at the output. I always get a 'idle' state, regardless of the OSSI bit (outputs OCx=OISx, OCxN=OISxN, except when simultaneously

OISx=not CCxP,

OISxN=not CCxNP).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-12 3:58 AM

Here is my code:

#include <stddef.h>

#include 'stm32f10x.h'

// Set state 'value' of bits of 'ref' by the mask.

template <typename T>

void assign_bit(T& ref, uint32_t mask, bool value){

if(value)

ref|=mask;

else

ref&=~mask;

}

// Set config. of TIM1.

void conf_tim1(bool moe, bool ossi, bool ossr,

bool ois1, bool ois1n,

bool cc1e, bool cc1ne, bool cc1p, bool cc1np,

bool oc1ref){

assign_bit(TIM1->BDTR, TIM_BDTR_OSSI, ossi);

assign_bit(TIM1->BDTR, TIM_BDTR_OSSR, ossr);

assign_bit(TIM1->CR2, TIM_CR2_OIS1, ois1);

assign_bit(TIM1->CR2, TIM_CR2_OIS1N, ois1n);

assign_bit(TIM1->CCER, TIM_CCER_CC1E, cc1e);

assign_bit(TIM1->CCER, TIM_CCER_CC1NE, cc1ne);

assign_bit(TIM1->CCER, TIM_CCER_CC1P, cc1p);

assign_bit(TIM1->CCER, TIM_CCER_CC1NP, cc1np);

// OC1M[2:0]=0x4 or OC1M[2:0]=0x5:

// force inactive level / force active level.

TIM1->CCMR1=((oc1ref)?0x5:0x4)<<4;

assign_bit(TIM1->BDTR, TIM_BDTR_MOE, moe);

}

void conf_tim1(uint32_t pack){

conf_tim1(pack&0x200, pack&0x100, pack&0x80,

pack&0x40, pack&0x20,

pack&0x10, pack&0x8, pack&0x4, pack&0x2,

pack&0x1);

}

int main(){

// Enable the necessary peripheral clock.

RCC->APB2ENR|=

RCC_APB2ENR_IOPAEN|

RCC_APB2ENR_IOPBEN|

RCC_APB2ENR_TIM1EN;

// PA8 (TIM1_CH1), PB13 (TIM1_CH1N):

// CNF.MODE=10=0xA (alt. out, push-pull, 2MHz max)

(GPIOA->CRH&=~0xF)|=0xA;

(GPIOB->CRH&=~(0xF<<(13-8)*4))|=0xA<<(13-8)*4;

// Try out possible combinations of configuration bits.

for(int i=0x000; i<=0x3FF; i++){

// Set configuration.

conf_tim1(i);

//Here we can check state of OC1, OC1N (PA8, PB13).

}

// Infinite loop

int j = 0;

while(true){

j++;

}

}

�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-12 12:25 PM

Below are the results of execution of my program.

Control bitsOutput states (OC1, OC1N)

MOEOSSIOSSRCC1E*CC1NE*OIS1OIS1Nif CC1P, CC1NP =

= 00 = 01 = 10 = 11

0

x

x

x

x

0

0

00

00

00

11

0

1

01

01

10

01

1

0

10

01

10

10

1

1

00

11

11

11

* These bits must not be zero at the same time, as in accordance with the manual:

When both outputs of a channel are not used (CCxE = CCxNE = 0), the OISx, OISxN, CCxP and CCxNP bits must be kept cleared.

So, the timer always acts as if OSSI=1.

If MOE==0 then

OC1=OIS1,

OC1N=OIS1N,

except when J==1, where J=(OIS1 xor CC1P) and (OIS1N xor CC1NP).

In other words, J==1 when both values OIS1, OIS1N correspond to the active levels (not CC1P, not CC1NP).

Finally we have that OC1=OIS1 xor J, OC1N=OIS1N xor J.

The question is why the behavior of the timer with OSSI = 0 does not match the one described in the manual?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-12 3:06 PM

As I said, I quoted from the RM0090 manual, which is for the 'F4.

As I said there, that table is not completed in RM0041, and this may be intentional.

JW