STM32L151VE ADC reads 20% lower value on one of the ADC inputs (channel 18, pin B12)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 1:48 AM

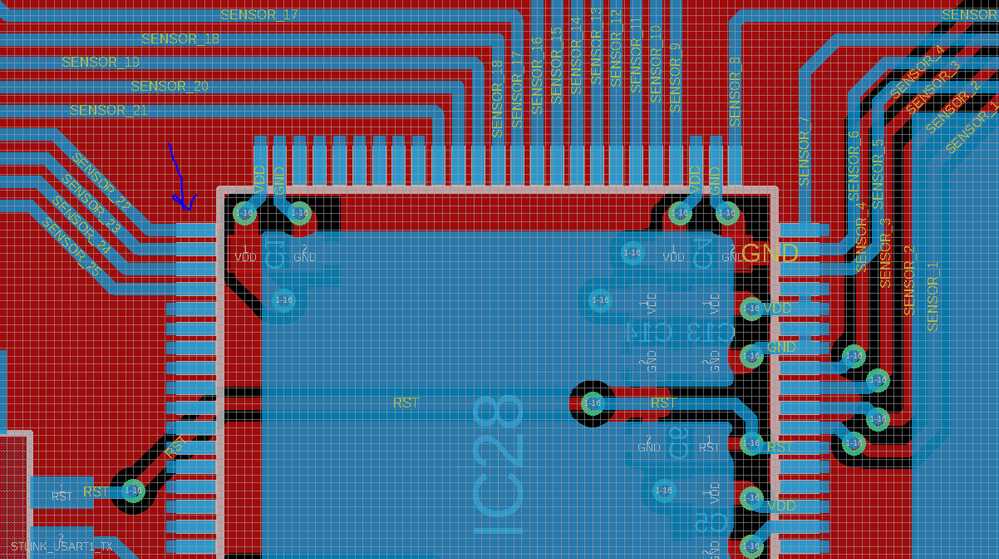

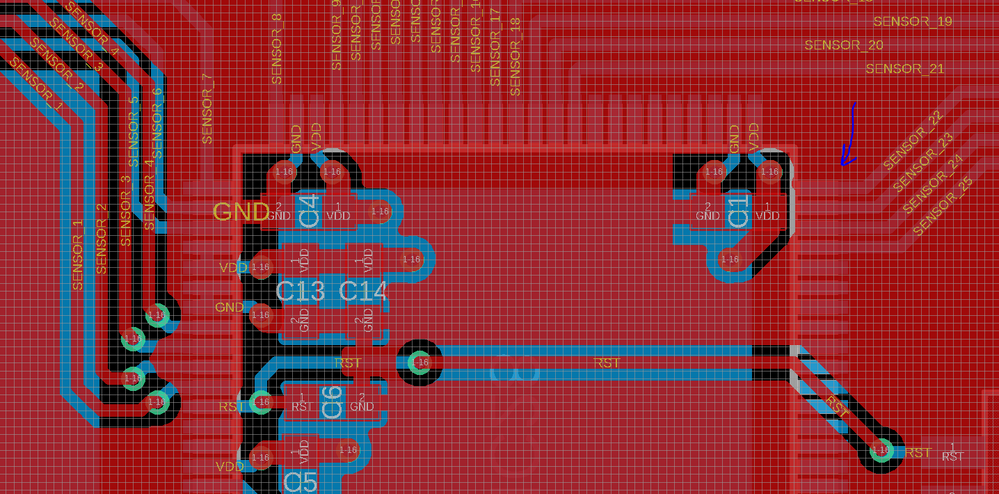

Not sure if I messed something up. Signal is okay (on the pin). No differences with layout compared to other inputs. ADC is at full speed (16 MHz).

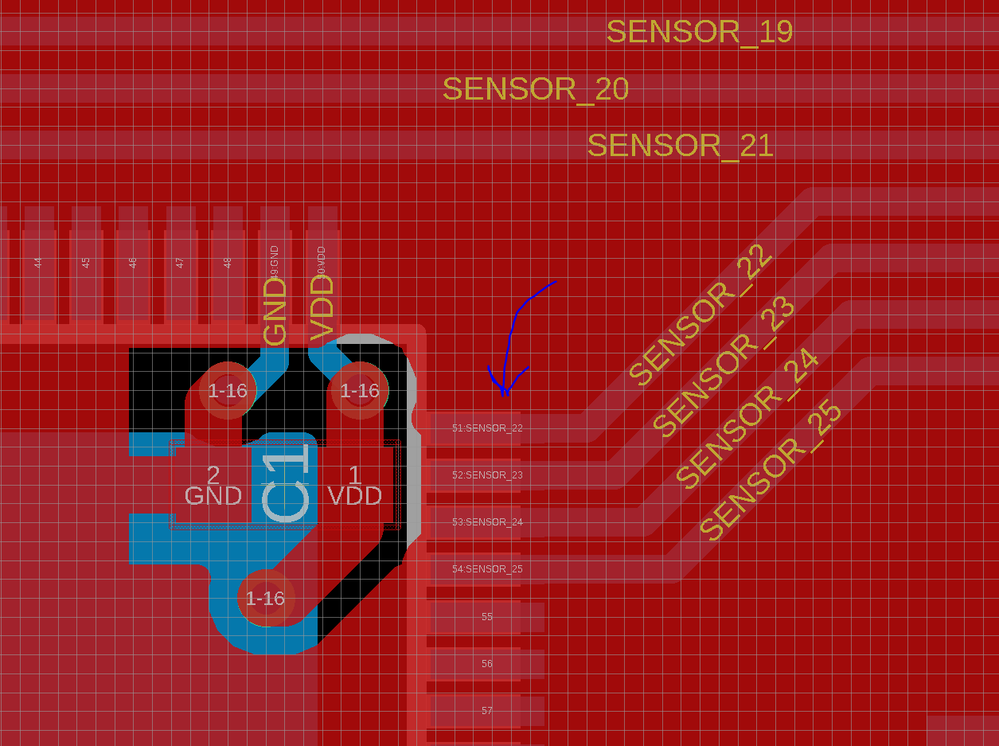

On image it is sensor 22 (reads ~2500). Sensor 23, 24, 25 all read normal values (~3000).

Voltages on all those pins is ~2.8V.

VREF, VDDA, VDD = 3.3V.

Solved! Go to Solution.

- Labels:

-

ADC

-

STM32L1 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 1:38 PM

Ok what you could do is set up the code to repeatedly measure just one ADC and measure the current through the VDDA pin. Repeat for the good and bad ADCs and see if there is a significant difference. Means lifting the pin but at least it's not a BGA. Can't think of anything else I'm afraid.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 3:04 AM

Your layout does not help to identify what Port Pins you use. How fast is your sampling? Maybe this is some issue with fast versus slow channels when sampling fast.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 3:18 AM

Exactly, there is a charge-up of the S&H capacitor involved.

Too short sample times create a "drag over" or pseudo-crosstalk effect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 11:31 AM

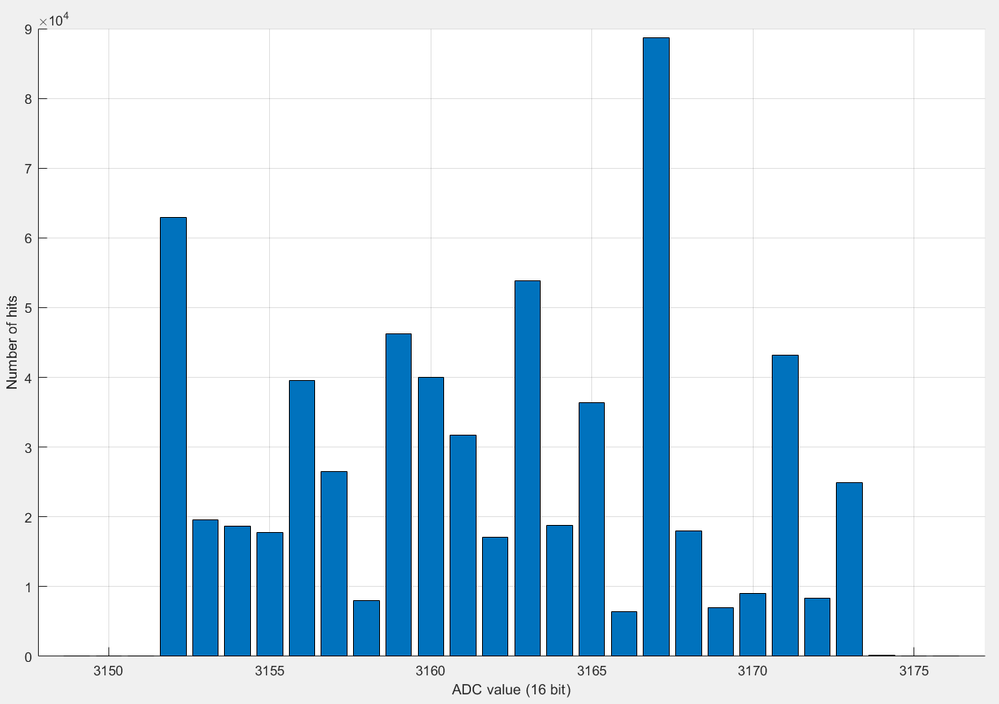

16 MHz (1 mega samples), 4 cycles sampling time.

Only 1 channel out of 24 which are all read in sequence reads lower value (consistently). I moved it around in a sequence but it didn't change anything.

Correction: sampling it multiple times does change the reading.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 11:38 AM

Similar problem with 16 cycles sampling time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 12:12 PM

Can we see the top side of the PCB ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 1:15 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 1:17 PM

Actually that's the best connected of the lot. Something the other end of the track maybe ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 1:20 PM

Have you examined the PCB with a magnifying glass and checked you don't have a manufacturing fault on that pin ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-13 1:25 PM

I checked signal on oscilloscope and it looks just fine. Both ends. Signal is low frequency, analog.

Not a lot of noise in signal lines.