Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Stm32f429 GPS PPS measuring

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Stm32f429 GPS PPS measuring

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-04-20 12:38 AM

Posted on April 20, 2016 at 09:38

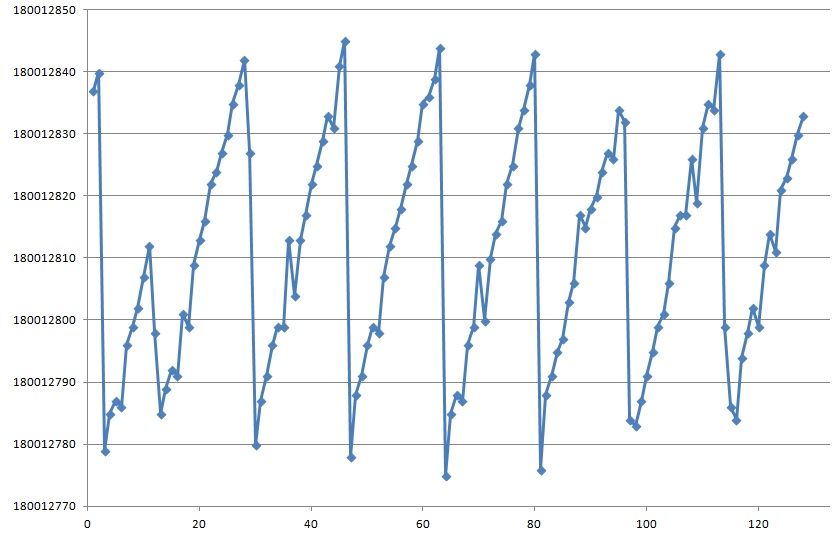

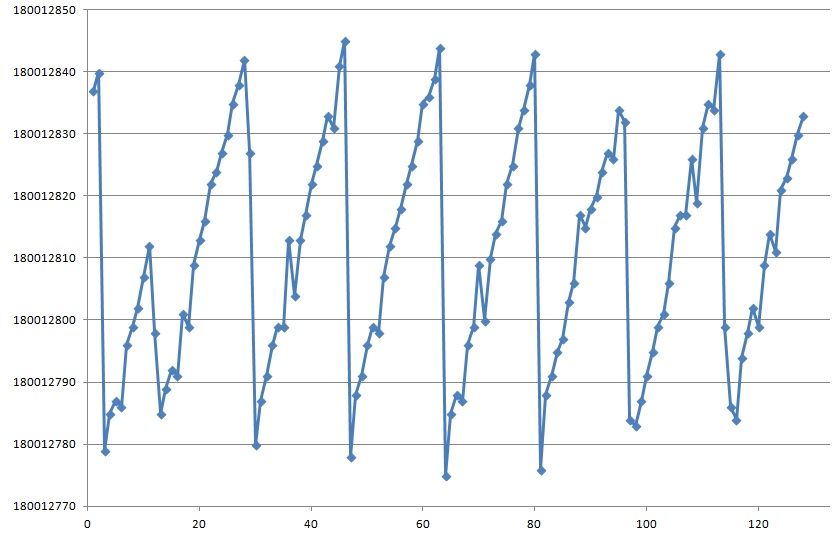

What caused this behavior?I apologize for not being word-perfect in English)

What caused this behavior?I apologize for not being word-perfect in English)

Hi! I try to measure GPS PPS (pulse per second) duration by TIM2. Setting code:

TIM_TimeBaseInitTypeDef TimeBaseInitStruct;

TIM_ICInitTypeDef ICInitStruct;

TimeBaseInitStruct.TIM_Prescaler = 0;

TimeBaseInitStruct.TIM_ClockDivision = TIM_CKD_DIV1;

TimeBaseInitStruct.TIM_CounterMode = TIM_CounterMode_Up;

TimeBaseInitStruct.TIM_Period = 0xFFFFFFFF;

TimeBaseInitStruct.TIM_RepetitionCounter = 0;

TIM_TimeBaseInit(PPS_IN_TIM, &TimeBaseInitStruct);

TIM_SelectInputTrigger(PPS_IN_TIM, TIM_TS_TI1FP1);

TIM_SelectMasterSlaveMode(PPS_IN_TIM, TIM_MasterSlaveMode_Enable);

TIM_SelectSlaveMode(PPS_IN_TIM, TIM_SlaveMode_Reset);

ICInitStruct.TIM_Channel = TIM_Channel_1;

ICInitStruct.TIM_ICPolarity = TIM_ICPolarity_Rising;

ICInitStruct.TIM_ICSelection = TIM_ICSelection_DirectTI;

ICInitStruct.TIM_ICPrescaler = TIM_ICPSC_DIV1;

ICInitStruct.TIM_ICFilter = 0;

TIM_ICInit(PPS_IN_TIM, &ICInitStruct); What caused this behavior?I apologize for not being word-perfect in English)

What caused this behavior?I apologize for not being word-perfect in English)

13 REPLIES 13

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-04-21 01:26 PM

Posted on April 21, 2016 at 22:26

Reviewing the number of seen satellites and quality of reception might be helpful. The accuracy of the PPS will surely degrade with fewer satellites.

Technically you only need one to understand the performance of the local clock (TCXO, crystal, or whatever). Even a relatively mediocre GPS receiver design can keep a 1PPS signal within a 100ns rms.Where one might expect the saw-tooth is the placement ability of the receiver, ie the granularity on the clock (10MHz 100ns), and it's drift, so it walks off, and periodically gets slewed back via one, or half a clock cycle of the internal synchronous machine.In specialized timing receivers, where you can discipline the local clock, you can pull the drift to zero effectively, and you have a time source down in the ppb range.

Tips, Buy me a coffee, or three.. PayPal Venmo

Up vote any posts that you find helpful, it shows what's working..

Up vote any posts that you find helpful, it shows what's working..

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-04-22 03:22 AM

Posted on April 22, 2016 at 12:22

Measuring 1 Hz meander from AFG3022C.

Measuring 1 Hz meander from AFG3022C.

I rewrote standart function

SetSysClock

on HSEstatic void SetSysClock(void)

{

/******************************************************************************/

/* PLL (clocked by HSE) used as System clock source */

/******************************************************************************/

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/* Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while ((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

/* Select regulator voltage output Scale 1 mode */

RCC->APB1ENR |= RCC_APB1ENR_PWREN;

PWR->CR |= PWR_CR_VOS;

/* HCLK = SYSCLK / 1*/

RCC->CFGR |= RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK / 2*/

RCC->CFGR |= RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK / 4*/

RCC->CFGR |= RCC_CFGR_PPRE1_DIV1;

PWR->CR |= PWR_CR_ODEN;

while ((PWR->CSR & PWR_CSR_ODRDY) == 0)

{

}

PWR->CR |= PWR_CR_ODSWEN;

while ((PWR->CSR & PWR_CSR_ODSWRDY) == 0)

{

}

/* Configure Flash prefetch, Instruction cache, Data cache and wait state */

FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN | FLASH_ACR_DCEN | FLASH_ACR_LATENCY_5WS;

/* Select the main PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

// RCC->CFGR |= RCC_CFGR_SW_PLL;

RCC->CFGR |= RCC_CFGR_SW_HSE;

/* Wait till the main PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != RCC_CFGR_SWS_HSE)

;

{

}

}

else

{ /* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}

} Measuring 1 Hz meander from AFG3022C.

Measuring 1 Hz meander from AFG3022C.

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-04-23 05:34 AM

Posted on April 23, 2016 at 14:34

- I rewrote standart function

SetSysClock

on HSE

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-05-04 04:07 AM

Posted on May 04, 2016 at 13:07 The SB18 and SB20 was mounted on board. I've removed them. i.e stm32f429Discovery incorrectly work from box.

The SB18 and SB20 was mounted on board. I've removed them. i.e stm32f429Discovery incorrectly work from box.

I've solved the problem.

The SB18 and SB20 was mounted on board. I've removed them. i.e stm32f429Discovery incorrectly work from box.

The SB18 and SB20 was mounted on board. I've removed them. i.e stm32f429Discovery incorrectly work from box.

- « Previous

-

- 1

- 2

- Next »

Related Content

- 8 simultaneous frequency measurements up to 2MHz on STM32U545REQ in STM32 MCUs Products

- ADC measuring only high side of Centered Mode PWM (HRTIM) in STM32 MCUs Products

- Measuring Clock Frequency in STM32 MCUs Boards and hardware tools

- TouchGFX Frame Buffer: image inverted at corners in STM32 MCUs TouchGFX and GUI

- Current measurement in STM32N6570-Discovery Kit in STM32 MCUs Boards and hardware tools