- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F412 QSPI problem when sending some bytes (OD...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F412 QSPI problem when sending some bytes (ODD) to external memory

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-17 8:06 AM

Hello everyone,

I'm trying to write and read some data with a NUCLEO f412 to an external memory in QSPI mode.

Following some examples I found on the web, I succeed into writing and reading some data from/to the external memory.

The memory is MX25L12835FM2I from Macronix (https://www.macronix.com/Lists/Datasheet/Attachments/7397/MX25L12835F,%203V,%20128Mb,%20v1.6.pdf)

The software is very simple (I'm using HAL library and True studio):

1) Write in the Status register of the memory the sixth bit in order to unlock the QSPI features.

2) erase entire memory (FF everywhere)

2) Send a byte array of data with the command 0x38 from address 0;

3) configure STM32 QSPI in memory mapped and read the data from address 0x90000000 with the command 0xEB

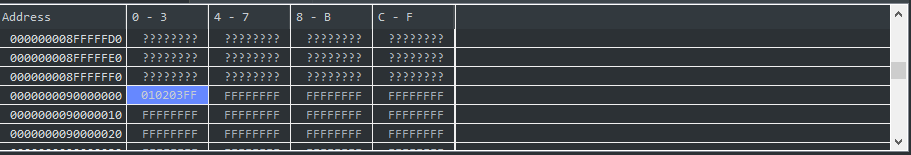

What I discovered is that when i look at the address 0x90000000 I dont always see the entire byte array i sent !

For example :

uint8_t aTxBuffer[] = {0x01,0x02,0x03,0x04,0x04,0x08,0x0A}If I send this array, the third byte (0x03) seems to block something in the software, in fact if I read the address 0x90000000 I find that after the 0x03 no more data is sent!

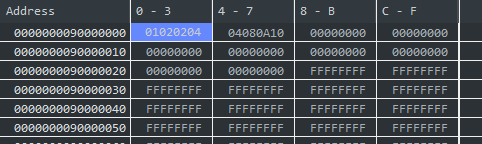

But if I change that 0x03 with another byte like 0x02, so:

uint8_t aTxBuffer[] = {0x01,0x02,0x02,0x04,0x04,0x08,0x0A};entire data is transmitted , and I can read it all!

I've set sCommand.NbData = 40, thats why some "0" are sent too..

I dont really understand where does this issue can come from... I mean just because I change a byte transferred, the program has to not work correctly?

I can give you further information:

1) I set dummycycle to 6 according to the memory datasheet, becouse bit 7 and 6 in configuration register of the memory are both zero

2) I tried to debug the Transmit phase, and i'm sure that entire byte array is transferred out

3) some other bytes are blocking (0x05,0x07,0x09, 0xAB, 0x47.......) ---> They are all ODD !

4) I tried both , Normal transfer and DMA transfer, same result.

I'll post entire code if necessary.

Thank you everyone

Andrea

- Labels:

-

QSPI

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-18 12:47 AM

Maybe you're mixing modes: QPI mode (for most manufacturers) means that *everything* (instruction, address, data) is sent/received on 4 lines. Whereas the 4PP command (0x38) you mentioned is sort of "mixed mode" command: instruction is sent on one line only, whereas address and data follow on 4 lines. The datasheet explicitly says that 4PP is SPI-only, whereas the standard PP (0x02) command adapts itself automatically to SPI- vs. QPI-mode.

You didn't mention the WREN command, but I suppose it's issued before every programming (including the WRSR) command?

BTW Bit 6 of status register enables QPI mode, not QSPI (the latter is ST's name for the interface in the MCU).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-01-18 3:50 AM

Man, many many thanks!!

I tought that QPI and QSPI were the same thing, now with the command 0x02, intruction 1line, address and data in4 lines, it works!!

Regards

Andrea

- stm32h723 lwip rtos,The client stops sending data after running for a period of time. It will only resume operation if an external device pings in STM32 MCUs Embedded software

- STM32H753I-EVAL2: HAL_SD_Init() fails at CMD55 with HAL_SD_ERROR_CMD_RSP_TIMEOUT in STM32 MCUs Embedded software

- STM32F4DISCOVERY DAC PA4/PA5 not reaching true 0V (shows ~0.045–0.05V) in STM32 MCUs Boards and hardware tools

- stm32h7 in Others: STM32 MCUs related

- WebSocket Server on STM32H7xx with Azure RTOS and NetXDuo — A Practical Guide in STM32 MCUs Embedded software