- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- stm32f302 ADC capture influences input signal

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

stm32f302 ADC capture influences input signal

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-02 10:38 PM

I'm testing stm32f302 ADC capture with DMA transfer, but get some strange issues.

I set the ADC1 to capture single channel AIN2(PA1) in continuous and DMA mode at 72MHz and 1.5 sample cycles.

Set the DAC1 output a fixed voltage of 2048 with VDDA = 3.3V at PA4.

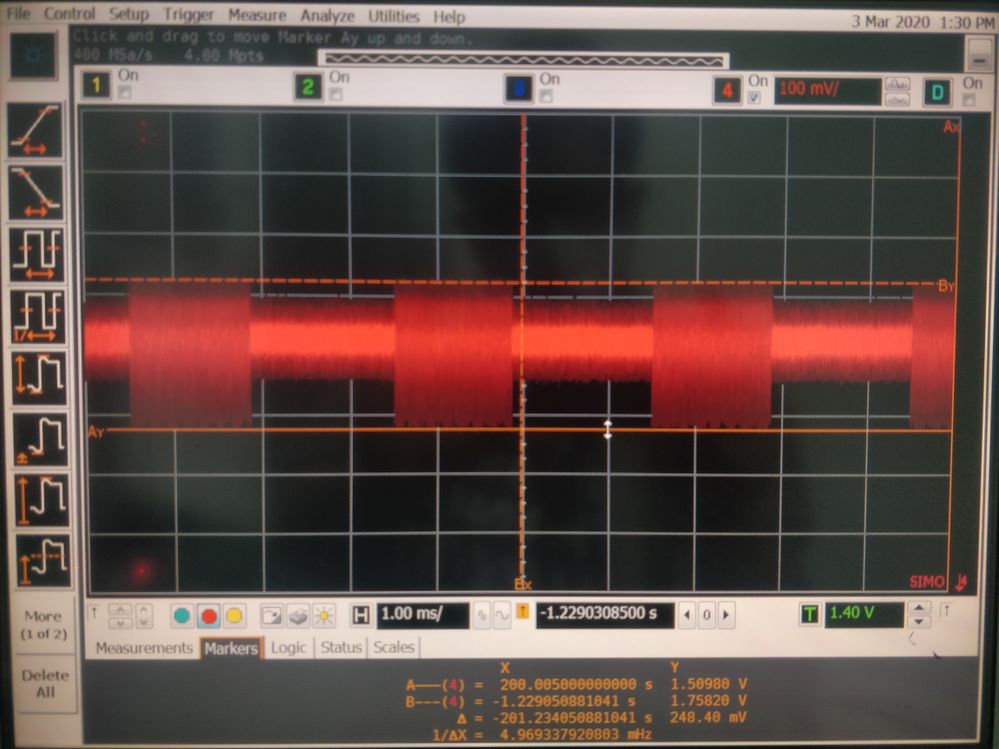

If I connect the PA4 to PA1 using a jumper, during the ADC capture, there will be a huge disturbance in PA4, about 248mVpp with 5.14MHz frequency.

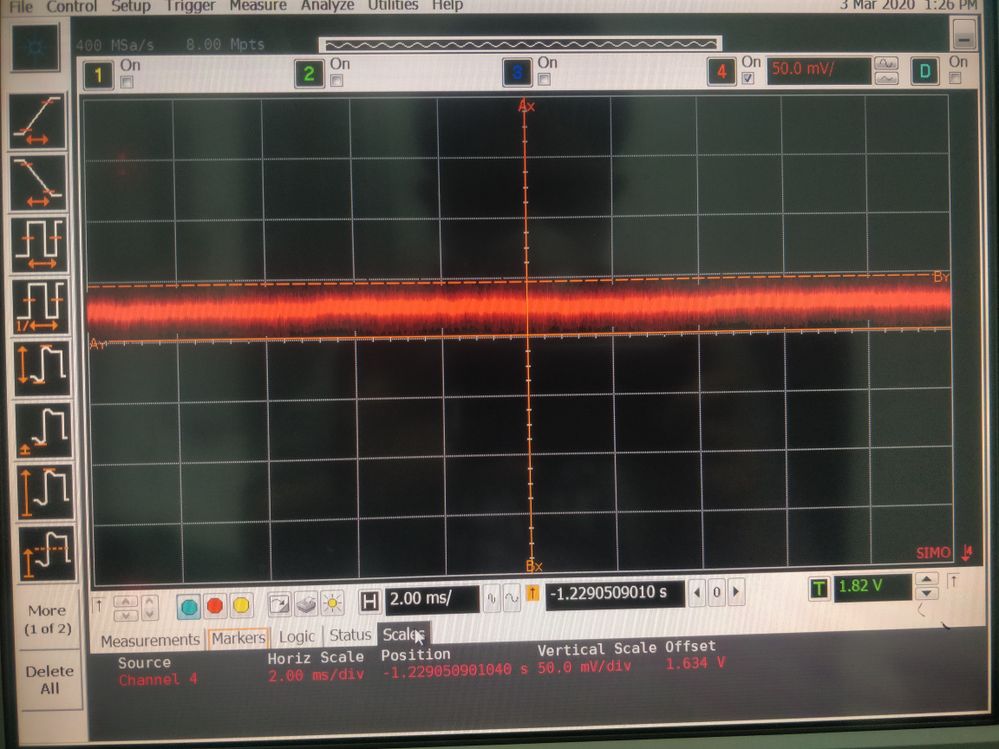

If stop the ADC capture or remove the jumper connection, there will be no these disturbances.

- Connect the PA4 to PA1 and start the ADC capture.

2. Disconnection PA4 and PA1 or stop the ADC capture.

Anybody has same issue or there are some bugs of ADC?

- Labels:

-

ADC

-

STM32F3 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-02 10:41 PM

The test board is NUCLEO-F302R8

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-02 10:52 PM

The ADC works as a capacitor with a few pF capacity (value specified in the datasheet), charged to half of VREF, which is at the beginning of the sampling phase connected to the input.

The DAC has a significant output impedance (depending on whether its output buffer is switched on or not). Again, for the particular value resort to the datasheet.

These two factors determine the "dip" in the input signal at the beginning of the ADC sampling phase.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-02 11:07 PM

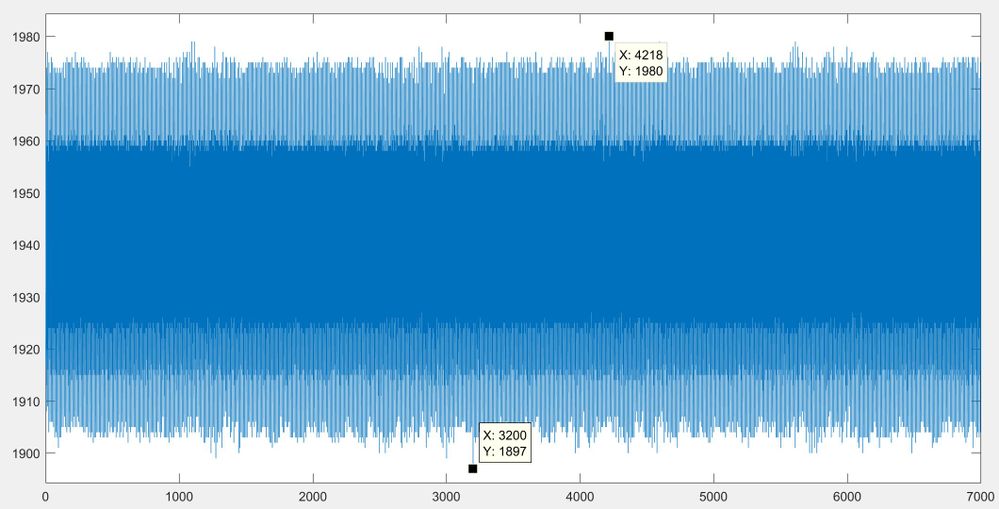

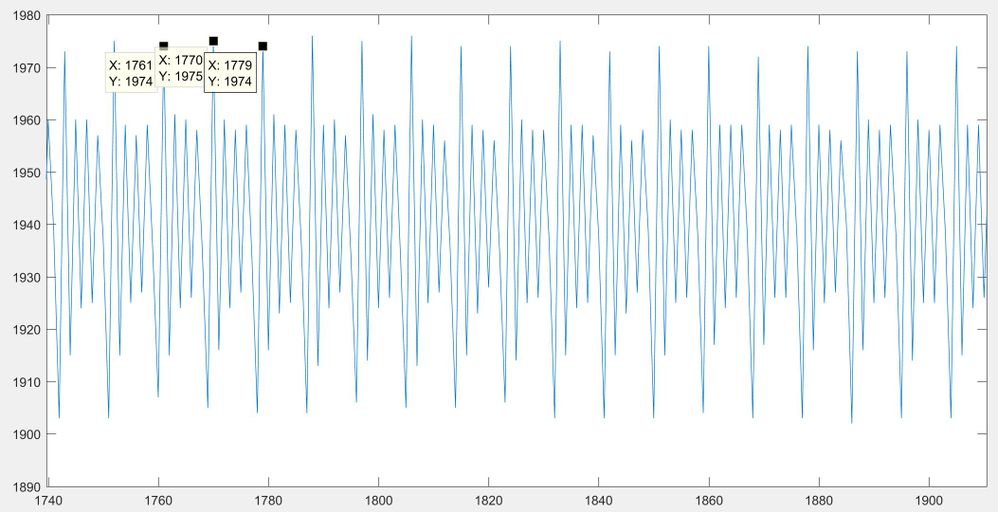

The output buffer is enabled. But the captured ADC data also has a huge noise about 83 code(peak-peak).

This doesn't make sense.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-02 11:22 PM

Try a different power supply.

Try a "known good" signal source, e.g. a common 1.5V AA battery.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-03 12:13 AM

A sample time of 1,5 cycles is extremely short. Is your input circuitry really up to that ?

> The output buffer is enabled.

With the output buffer enabled, the DAC has up to 200mV offset.

Check the datasheet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-03 12:47 AM

Yes, I need 4-5MSPS to capture a 600kHz sine wave. And I try to increase the sample time to 181.5, this issue still exists.

Additionally, I add a extra OPAMP1 in Follower mode as a buffer. But the result is same.

I have never seen this issue in Cypress, TI MSP430 ADC.

I don't care the offset. The offset is a fixed value which can be calibrated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-03 1:23 AM

> Yes, I need 4-5MSPS to capture a 600kHz sine wave.

That's fine, just wanted to mention that. The design/selection of an appropriate input buffer for 5MSps is a non-trivial task.

For the DAC part, did you see the bandwidth specs ?

This device is IMHO not up to the task.

I would try a proper source for the 600kHz sine signal.