- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: spi clock error in STM32L431

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

spi clock error in STM32L431

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-10 12:32 AM

hi,I want use SPI1 as master and SPI1 reg configure as that

SPI1->CR2 =

0x1704

; SPI1->CR1 =0x15C

;read code is

GPIOA->BSRR |=

1

<<20

;//set NSS low

for

(i =0

;i < command_size;i++){

while

(0

== (SPI1->SR & SPI_SR_TXE)); SPI1->DR = out_buf[

i]

&0xFF

;while

(0

== (SPI1->SR & SPI_SR_RXNE)); in_buf[

i]

= SPI1->DR &0xFF

;}

GPIOA->BSRR |=1

<<4

;//set NSS high

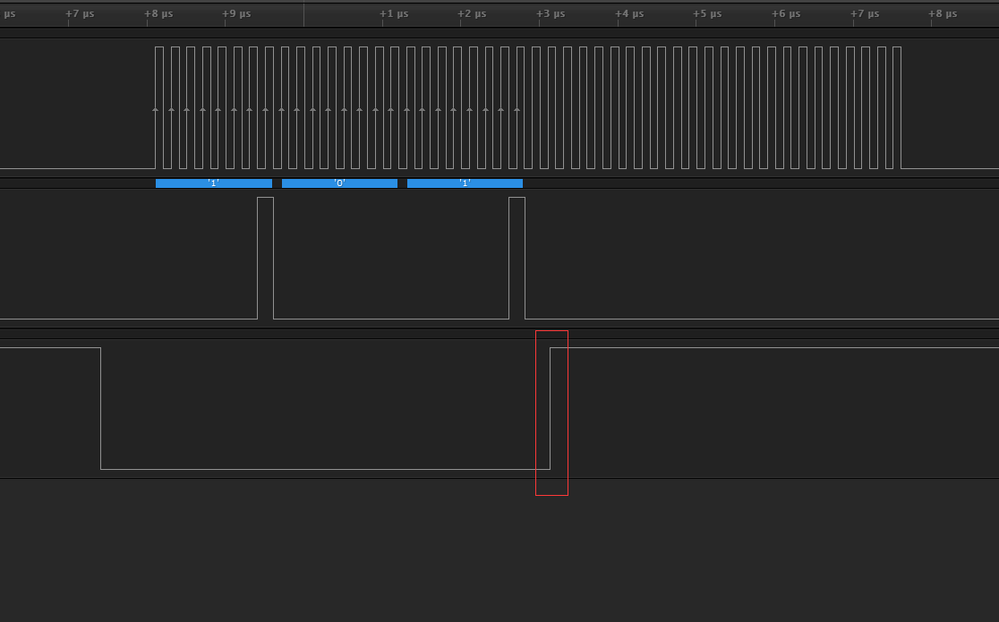

i use logic analyzer capture the logic as

it saw that clock also driver after NSS set high.

can anyone help me

#stm32l431-spiSolved! Go to Solution.

- Labels:

-

STM32L4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-10 02:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-10 12:56 AM

Release NSS only when SPI BUSY bit is cleared.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-10 02:00 AM

thank you for reply, my problem is that when i send 3 bytes but it have 48 clocks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-10 02:27 AM

- sdio not working in STM32 MCUs Products

- STM32C07: Jump to STM Bootloader but can't erase or change anything in STM32 MCUs Products

- CAN START Probem in STM32 MCUs Products

- Code Debugging using STLINKV2 in STM32 MCUs Boards and hardware tools

- stm32wle5ccu6 stopmode disables programming in STM32 MCUs Products