- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- How to use Interrupt enable Registers?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to use Interrupt enable Registers?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-11 9:15 AM

In Cortex m3/m4, Interrupt Set Enable Registers is used to enable/disable the interrupts. How would we know which bit corresponds to which interrupt?

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0553a/Cihcajhj.html

does not give a clue on this.#interrupt-handler #stm #stm32f103 #interrupt-issue- Labels:

-

Interrupt

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-11 12:32 PM

The NVIC interrupts are implementation specific (ie ST, ATMEL, NXP, etc), so look at the Reference Manual for the part you are using.

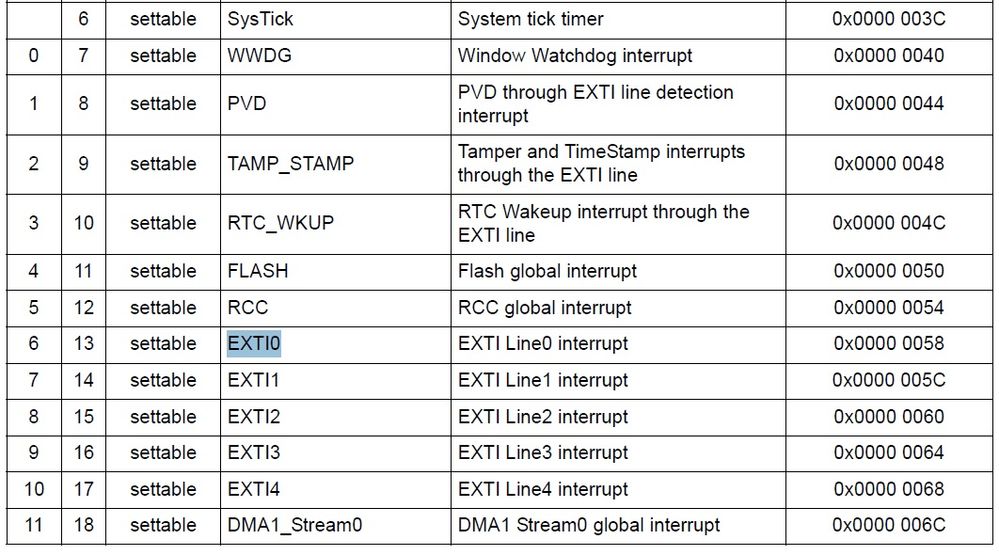

Review Vector Table, there is a linear application of bits and registers within the NVIC

So EXTI0 is interrupt #6

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-11 2:04 PM

,

,

So this means if I want to enable hardfault and memManage Fault, which is interrupt no. 3 and 4 according to

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0553a/BABIFJFG.html

, ,I can simply do this,♯ define NVIC_ISER (*((volatile unsigned long*) 0xE000E100))

NVIC_ISER = 0x00000018, // Interrupt set enable register

Right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-11 3:44 PM

>>Right?

No, they are SYSTEM EXCEPTIONS, not INTERRUPTS (IRQs)

The IRQs are in the NVIC, the System Exceptions are not. In the table above IRQ ♯ 0 is WWDG, IRQ ♯ 3 is RTC_WKUP

http://infocenter.arm.com/help/topic/com.arm.doc.dui0553a/Cihhjgdh.html

Use SCB->SHSCR |= (1 << 16); to enable the Memory Manager

Would suggest ORing new bits on to registers rather than assuming initial/current content

Up vote any posts that you find helpful, it shows what's working..

- Ask for I3C support on NUCLEO-H563ZI (MB1404C) in STM32 MCUs Embedded software

- STM32U575VGT: Autonomous SPI reading in STM32 MCUs Embedded software

- STM32F767 I2C sending byte immediately after address sent in STM32 MCUs Products

- STM32U535 LPBAM LPTIM3 capture problem in STM32 MCUs Embedded software

- Recommended way to transmit "small" data frames of different lengths over SPI in STM32 MCUs Embedded software