- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- How to set up APS512XX RAM in 1K burst mode on the...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to set up APS512XX RAM in 1K burst mode on the STM32U5A9J-DK board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-14 4:31 PM

I am trying to set up the on-board 512Mb AP PSRAM to have a 1K word linear read burst.

Similar to the HSPI demo in the BSP example, I call the function "BSP_HSPI_RAM_Config16BitsOctalRAM(...)"

with my configuration set to use a 1K word linear burst.

However, the implementation of this function in the file 'stm32u5x9j_discovery_hspi.c' contains this conditional check at the very beginning of the function:

/* Check if the instance is supported */

if ((Instance >= HSPI_RAM_INSTANCES_NUMBER)

|| (Cfg->BurstLength == APS512XX_BURST_2_KBYTES))

{

ret = BSP_ERROR_WRONG_PARAM;

}

Solved! Go to Solution.

- Labels:

-

STM32U5 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-22 2:53 AM - edited 2023-11-22 3:04 AM

Hi @RMand ,

I apologize that my comments didn't answer your question.

4- I am also noticing that the driver ignores bursts that are NOT HYBRID and sets up the HAL RAM configuration as 'HAL_XSPI_WRAP_NOT_SUPPORTED'. Should I understand this as saying that the HSPI does not work well in non-hybrid wrap modes?

The HSPI interface supports the non-hybrid wrap mode.

This particular case is used when the external memory device does not support hybrid wrap mode.

The HAL drivers doesn't support directly the non-hybrid mode.

So, to configure this mode, you needs to set:

- The HAL configuration as 'HAL_XSPI_WRAP_NOT_SUPPORTED'

- The appropriate configuration parameters in the HSPI registers and configure the command.

I hope this answer your request.

Thank you.

Kaouthar

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-14 4:43 PM

I realize now that the HSPI (in memory mapped mode at the least) only supports upto 64-bytes wrap/burst mode and that is why the function bails out when presented with a 1K burst size.

Can somebody confirm this to be the case?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-15 1:03 AM

Hello @RMand ,

Only in memory mapped mode :

- Illegal wrap size when receiving read wrap burst with size different from 48 bytes.

- Illegal access size when wrap read burst. This means HSIZE is different from 4 bytes.

For more information, I advise you to refer to the RM0456 and precisely sections: 30.4.17 HSPI error management and 30.7.3 HSPI device configuration register 2.

Thank you.

Kaouthar

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-15 10:36 AM - edited 2023-11-15 12:06 PM

Hi Kouthar

Thanks for your response but I do have some questions for you.

- How do I set '48 bytes' for the read wrap burst -- I do not see an option for this value in the driver files.

- Section 30.4.17 of RM0456 talks about managing the HSPI errors in memory mapped mode at RUN TIME. The failure I was observing was when trying to configure the HSPI -- even before I ever got it to run in memory mapped mode.

- The CubeMX generates template code that sets the value of 'DEVSIZE' in HSPI DCR1 to 26 for this design kit board that includes a 64MB HSPI PSRAM.

*** BUT ***

The note in RM0456 for HSPI DCR1 says that the size of the external memory address is calculated and expected to be 2^(DEVSIZE+1). If DEVSIZE is 26 then this would evaluate to 128MB.

CLEARLY SOMETHING IS NOT CONSISTENT -- who should I now believe -- the CubeMX or the folks that wrote up RM0456? - I am also noticing that the driver ignores bursts that are NOT HYBRID and sets up the HAL RAM configuration as 'HAL_XSPI_WRAP_NOT_SUPPORTED'. Should I understand this as saying that the HSPI does not work well in non-hybrid wrap modes?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-16 9:17 AM - edited 2023-11-17 6:27 AM

Hello @RMand ,

1-2- When checking the HSPI error management section, I noted a typo about wrap size condition:

- an illegal wrap size when receiving read wrap burst with size different from 48 bytes (only for memory-mapped mode)

Should be

- an illegal wrap size when receiving read wrap burst with size different from 4 bytes (only for memory-mapped mode).

Thank you for bringing this issue to our attention and sorry for any inconvenience.

I reported this typo internally.

Internal ticket number: 166594 (This is an internal tracking number and is not accessible or usable by customers).

How do I set '48 bytes' for the read wrap burst? -->Which master did you use? Dcache? Icache?

I think the AN5212 can help you.

3- The Device Size configured in STM32Cube MX indicates the size of the OSPI memory in bytes and expressed in 2^n.

How to configure "Device Size" in STM32CubeMX is descripted in How to set up the OSPI peripheral to interface with the IS25LX256 from ISSI and in table Table 7. STM32CubeMX - Configuration of OCTOSPI parameters in AN5050.

The device size configuration is down in the HAL_XSPI_Init function by using this code

/* Configure memory type, device size, chip select high time, free running clock, clock mode */

MODIFY_REG(hxspi->Instance->DCR1,

(XSPI_DCR1_MTYP | XSPI_DCR1_DEVSIZE | XSPI_DCR1_CSHT | XSPI_DCR1_FRCK | XSPI_DCR1_CKMODE),

(hxspi->Init.MemoryType | ((hxspi->Init.MemorySize) << XSPI_DCR1_DEVSIZE_Pos) |

((hxspi->Init.ChipSelectHighTimeCycle - 1U) << XSPI_DCR1_CSHT_Pos) | hxspi->Init.ClockMode));

So, the DEVSIZE bits filed in XSPI_DCR1 registers get the Init.DeviceSize (configured in ioc file) - 1U, which is in line with RM0456 description.

In conclusion the "Device Size" in STM32cubeMX is DCR1_DEVSIZE+1.

For more explanation I advice you to refer to this discussion.

4- The HSPI support the wrap feature as described in RM0456.

Thank you.

Kaouthar

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-20 3:37 PM

Hi

Thanks for your responses.

Regarding question 3, I believe I incorrectly interpreted the output code and it is in fact correct.

Regarding question 4:

YES, I am aware that HSPI does support hybrid mode. But I am curious as to why the HAL 'ignores bursts that are not HYBYRID'. This implies that the application MUST ALWAYS program the HSPI in hybrid mode.

Cheers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-21 12:08 AM

Hi @RMand ,

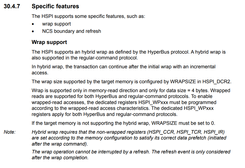

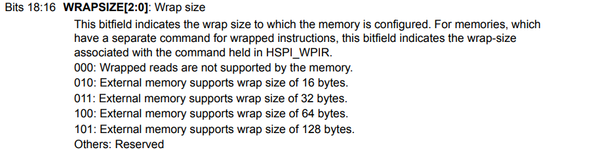

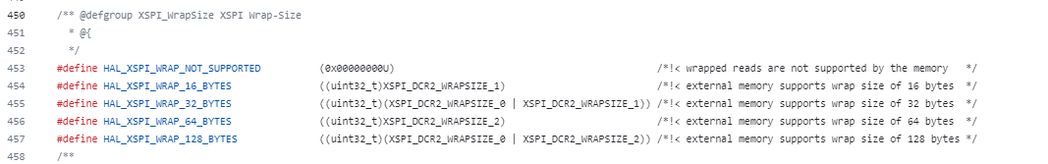

About the question 4: The HSPI supports an hybrid wrap and the wrap size is supported by configured WRAPSIZE in HSPI_DCR2:

This configuration is described in the stm32u5xx_hal_xspi.h Hal drivers:

Thanks and best regards,

Kaouthar

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-21 2:03 PM

I am not sure how many more times I have to ask you the same question:

Why is the application being FORCED TO USE THE HYBRID mode in HSPI?

The way it is set up now, if the application choses NOT TO USE HYBRID MODE then this HAL driver DOES NOT GET THE JOB DONE AND CANNOT BE USED.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-22 2:53 AM - edited 2023-11-22 3:04 AM

Hi @RMand ,

I apologize that my comments didn't answer your question.

4- I am also noticing that the driver ignores bursts that are NOT HYBRID and sets up the HAL RAM configuration as 'HAL_XSPI_WRAP_NOT_SUPPORTED'. Should I understand this as saying that the HSPI does not work well in non-hybrid wrap modes?

The HSPI interface supports the non-hybrid wrap mode.

This particular case is used when the external memory device does not support hybrid wrap mode.

The HAL drivers doesn't support directly the non-hybrid mode.

So, to configure this mode, you needs to set:

- The HAL configuration as 'HAL_XSPI_WRAP_NOT_SUPPORTED'

- The appropriate configuration parameters in the HSPI registers and configure the command.

I hope this answer your request.

Thank you.

Kaouthar

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.