- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: How do I specify memory region in STM32F103RB ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How do I specify memory region in STM32F103RB Micro-Controller?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-08 10:51 AM

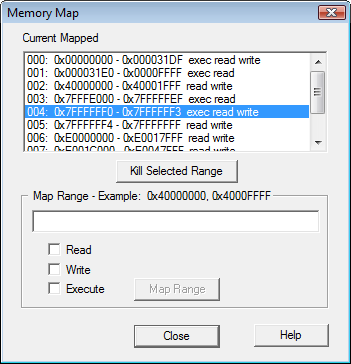

In Keil uvision I can define a memory region by using MAP command.

MAP 0x3FFFFB44,0x3FFFFFF8 read write

Or

I could use the Memory Map dialog from Keil ''Debug'' dropdown.

However, what should I do to specify the memory region in actual hardware (in my case STM32F103RB)?

Is there a way to specify a memory region in STM32 ST-LINK Utility software before burning code in my stm32 microcontroller?

NOTE:

I want to be able to read/write in a memory region from 0x3FFFFB44,0x3FFFFFF8 which is inaccessible. Everything works fine in Keil Simulator after I add this memory region range in Memory Map dialog. What should I do to be able to access this region in actual hardware?Thanks

#keil #memory #stm32f103rb- Labels:

-

Keil

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-08 11:59 AM

You don't get to define this, you can add external memory to STM32 devices via the FSMC/FMC bus, but the decode addresses are fixed by the hardware, no doubt described in the Reference Manuals

On the STM32F1 your FLASH memory is situated at 0x08000000 and the SRAM at 0x20000000, with the peripherals up at 0x40000000

In your compiler/linker settings you should specify the memory map the code needs to use

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-09 5:10 AM

So, I have specified memory region of 1204 bytes starting from

0x3FFFFB44

inside Stm32Flash.ld file. This is my Flash.ld file after configuring it./*

********************************************************************************* File : stm32_flash.ld**** Abstract : Linker script for STM32F103VB Device with** 128KByte FLASH, 20KByte RAM**** Set heap size, stack size and stack location according** to application requirements.**** Set memory bank area and size if external memory is used.**** Target : STMicroelectronics STM32**** Environment : Atollic TrueSTUDIO(R)**** Distribution: The file is distributed “as is,� without any warranty** of any kind.**** (c)Copyright Atollic AB.** You may use this file as-is or modify it according to the needs of your** project. Distribution of this file (unmodified or modified) is not** permitted. Atollic AB permit registered Atollic TrueSTUDIO(R) users the** rights to distribute the assembled, compiled & linked contents of this** file as part of an application binary file, provided that it is built** using the Atollic TrueSTUDIO(R) toolchain.********************************************************************************//* Entry Point */

ENTRY(Reset_Handler)/* Highest address of the user mode stack */

_estack = 0x20005000; /* end of 20K RAM *//* Generate a link error if heap and stack don't fit into RAM */

_Min_Heap_Size = 0; /* required amount of heap */_Min_Stack_Size = 0x100; /* required amount of stack *//* Specify the memory areas */

MEMORY{ FLASH (rx) : ORIGIN = 0x08000000, LENGTH = 128K RAM (xrw) : ORIGIN = 0x20000000, LENGTH = 20K SRAM (rwx) : ORIGIN = 0x3FFFFB44, LENGTH = 1204B MEMORY_B1 (rx) : ORIGIN = 0x60000000, LENGTH = 0K}/* Define output sections */

SECTIONS{ /* The startup code goes first into FLASH */ .isr_vector : { . = ALIGN(4); KEEP(*(.isr_vector)) /* Startup code */ . = ALIGN(4); } >FLASH/* The program code and other data goes into FLASH */

.text : { . = ALIGN(4); *(.text) /* .text sections (code) */ *(.text*) /* .text* sections (code) */ *(.rodata) /* .rodata sections (constants, strings, etc.) */ *(.rodata*) /* .rodata* sections (constants, strings, etc.) */ *(.glue_7) /* glue arm to thumb code */ *(.glue_7t) /* glue thumb to arm code */KEEP (*(.init))

KEEP (*(.fini)). = ALIGN(4);

_etext = .; /* define a global symbols at end of code */ } >FLASH .ARM.extab : { *(.ARM.extab* .gnu.linkonce.armextab.*) } >FLASH .ARM : { __exidx_start = .; *(.ARM.exidx*) __exidx_end = .; } >FLASH.ARM.attributes : { *(.ARM.attributes) } > FLASH

.preinit_array :

{ PROVIDE_HIDDEN (__preinit_array_start = .); KEEP (*(.preinit_array*)) PROVIDE_HIDDEN (__preinit_array_end = .); } >FLASH .init_array : { PROVIDE_HIDDEN (__init_array_start = .); KEEP (*(SORT(.init_array.*))) KEEP (*(.init_array*)) PROVIDE_HIDDEN (__init_array_end = .); } >FLASH .fini_array : { PROVIDE_HIDDEN (__fini_array_start = .); KEEP (*(.fini_array*)) KEEP (*(SORT(.fini_array.*))) PROVIDE_HIDDEN (__fini_array_end = .); } >FLASH/* used by the startup to initialize data */

_sidata = .;/* Initialized data sections goes into RAM, load LMA copy after code */

.data : AT ( _sidata ) { . = ALIGN(4); _sdata = .; /* create a global symbol at data start */ *(.data) /* .data sections */ *(.data*) /* .data* sections */. = ALIGN(4);

_edata = .; /* define a global symbol at data end */ } >RAM/* Uninitialized data section */

. = ALIGN(4); .bss : { /* This is used by the startup in order to initialize the .bss secion */ _sbss = .; /* define a global symbol at bss start */ __bss_start__ = _sbss; *(.bss) *(.bss*) *(COMMON). = ALIGN(4);

_ebss = .; /* define a global symbol at bss end */ __bss_end__ = _ebss; } >RAMPROVIDE ( end = _ebss );

PROVIDE ( _end = _ebss );/* User_heap_stack section, used to check that there is enough RAM left */

._user_heap_stack : { . = ALIGN(4); . = . + _Min_Heap_Size; . = . + _Min_Stack_Size; . = ALIGN(4); } >RAM/* MEMORY_bank1 section, code must be located here explicitly */

/* Example: extern int foo(void) __attribute__ ((section ('.mb1text'))); */ .memory_b1_text : { *(.mb1text) /* .mb1text sections (code) */ *(.mb1text*) /* .mb1text* sections (code) */ *(.mb1rodata) /* read-only data (constants) */ *(.mb1rodata*) } >MEMORY_B1/* Remove information from the standard libraries */

/DISCARD/ : { libc.a ( * ) libm.a ( * ) libgcc.a ( * ) }}Now at this point, I don't need to specify memory manually inside

Memory Map dialog, Right?

When I run the program it still gives me the access violation at 0x3FFFFB44. Am I configuring the Flash.ld file correctly?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-09 9:40 AM

>>Now at this point, I don't need to specify memory manually inside

Memory Map dialog, Right?

You're telling the linker where it can place things, not sure that's the same thing you were doing with the Simulator

>>When I run the program it still gives me the access violation at 0x3FFFFB44. Am I configuring the Flash.ld file correctly?

The .LD describes what you want the linker to do.

The STM32F1 still doesn't have any memory in that region, and generates a fault because you access something that doesn't exist.

This memory space is a fiction of your imagination, it doesn't exist in reality. The silicon design in the chip does not include it.

While the chip has a notional 4GB address space (0.. 0xFFFFFFFF) there are large holes in that.

Up vote any posts that you find helpful, it shows what's working..

- How can I make toggle buttons that will generate a trigger as long as they're on and will turn off automatically at a set time in STM32 MCUs TouchGFX and GUI

- Reading continuous data from an external ADC with SPI at a high sample rate in STM32 MCUs Products

- primary bootloader in STM32 MCUs Products

- Live Expression is not showing / not updating in stm32cubeIDE-version-1.15.1 in STM32CubeIDE (MCUs)

- Writing and reading external parallel flash with STM32 in STM32 MCUs Products