- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- F4 I2S read only first frame is valid

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

F4 I2S read only first frame is valid

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-31 2:54 PM

I'm trying to read i2s data on F401 from a dummy master device with slow clock rate.

The problem is that it only reads the first channel correctly, rest is gibberish, based on logic analyzer the rest of data is there.

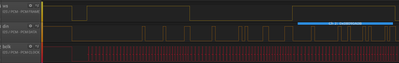

so I generate this simple test data with bitbang going into F401, content should be: 0001 0203, 0405 0607, 0809 0A0B (only last is displayed)

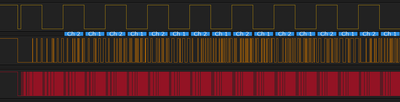

zoomed out:

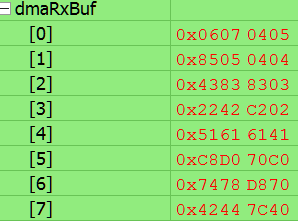

what I read in F401 is:

It starts to receive from second frame, that's fine, but why is the rest gibberish if data seems right?

Weird part is that during every test I get the same invalid values, like if it desyncronises everytime the same way.

#define DMA_BUFF_LEN 8

static volatile int32_t dmaRxBuf[DMA_BUFF_LEN+1];

static I2S_HandleTypeDef hi2s2;

__HAL_RCC_SPI2_CLK_ENABLE();

hi2s2.Instance = SPI2;

hi2s2.Init.Mode = I2S_MODE_SLAVE_RX;

hi2s2.Init.Standard = I2S_STANDARD_PHILIPS;

hi2s2.Init.DataFormat = I2S_DATAFORMAT_32B;

hi2s2.Init.MCLKOutput = I2S_MCLKOUTPUT_DISABLE;

hi2s2.Init.AudioFreq = I2S_AUDIOFREQ_44K;

hi2s2.Init.CPOL = I2S_CPOL_LOW; /* idle low clock */

hi2s2.Init.ClockSource = I2S_CLOCK_EXTERNAL; /* not PLL */

hi2s2.Init.FullDuplexMode = I2S_FULLDUPLEXMODE_ENABLE;

/* errata: i2s must be enabled during WS is high */

while(BIT_ISCLR(GPIOB->IDR, BIT32(12)));

ASSERT(HAL_I2S_Init(&hi2s2) == HAL_OK);

ASSERT(HAL_I2S_Receive(&hi2s2, (tUI16 *)dmaRxBuf, DMA_BUFF_LEN, 10u) == HAL_OK);return values pass, this is simple polling not even DMA.

After receiving this is the SPI2/I2S register status

Not sure why the overrun error, since I do polling mode, and BCLK is slow bitbanged 19Khz.

Solved! Go to Solution.

- Labels:

-

I2S

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-01 3:28 AM

> I bitbanged a valid I2S stream

100% sure ?

>WS frame: 1empty clock, then 32clock for data

But should be 31 clks , then WS switching, then 32. clk ; then next 31 clks, then WS switching, then 32. clk , ...

(Maybe thats what makes OV .)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-31 3:02 PM

What is this : > from a dummy master device < ?

-- has to do timing, bck, wck, ..data according to your settings for I2S2 .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-01 2:50 AM

On a 2nd MCU I bitbanged a valid I2S stream, that's what you can see on first 2 images, with slow BCK, and known data pattern.

Why would it read part of it correctly then rest as nonsense?

WS frame: 1empty clock, then 32clock for data,

data on rising clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-01 3:28 AM

> I bitbanged a valid I2S stream

100% sure ?

>WS frame: 1empty clock, then 32clock for data

But should be 31 clks , then WS switching, then 32. clk ; then next 31 clks, then WS switching, then 32. clk , ...

(Maybe thats what makes OV .)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-01 2:37 PM - edited 2024-02-01 2:38 PM

My mistake, first bit is last WS's LSB, seems like an unelegant design.

HAL_I2S_Receive can still receive only first one, for some reason it doesn't like it if more packets follow.

Anyway, DMA works great instead of polling.

- TouchGFX Application Shows Black Screen After Bootloader Jump in STM32 MCUs TouchGFX and GUI

- Dynamic Graph Hard Fault with Large Data Points in STM32 MCUs TouchGFX and GUI

- STM32 + Freertos + Audio recording + FATFS. Audio really choppy and white noisy in STM32 MCUs Embedded software

- STM32N6570-DK – Ethernet TX Failure & Camera Frame Not Received in STM32 MCUs Embedded software

- GPDMA in Linked List with OCTOSPI in STM32 MCUs Embedded software