DMA transfer error in STM32H7 DCMI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-13 12:55 PM

Hi all,

I am trying to setup a DCMI example with NUCLEO-H743ZI, the DCMI interrupts work fine, but DMA abrot when transferring the first data and TEIF is set.

The project was setup with CubeMX, and more detail changes is in the git log. I didn't use cache and I've tried to align the buffer, but the problem remains. The Reference manual suggests the following, but I can't figure out what's wrong and how to fix it.

The transfer error interrupt flag (TEIF) is set when:

• A bus error occurs during a MDMA read or a write access

• The address alignment does not correspond to the data size

• The block size is not a multiple of the data size (for source and/or destination): this error is activated on the last transfer and the error address points to the last transfer (which cannot be done)

Any help and suggestions will be greatly appreciated.

Solved! Go to Solution.

- Labels:

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-13 2:49 PM

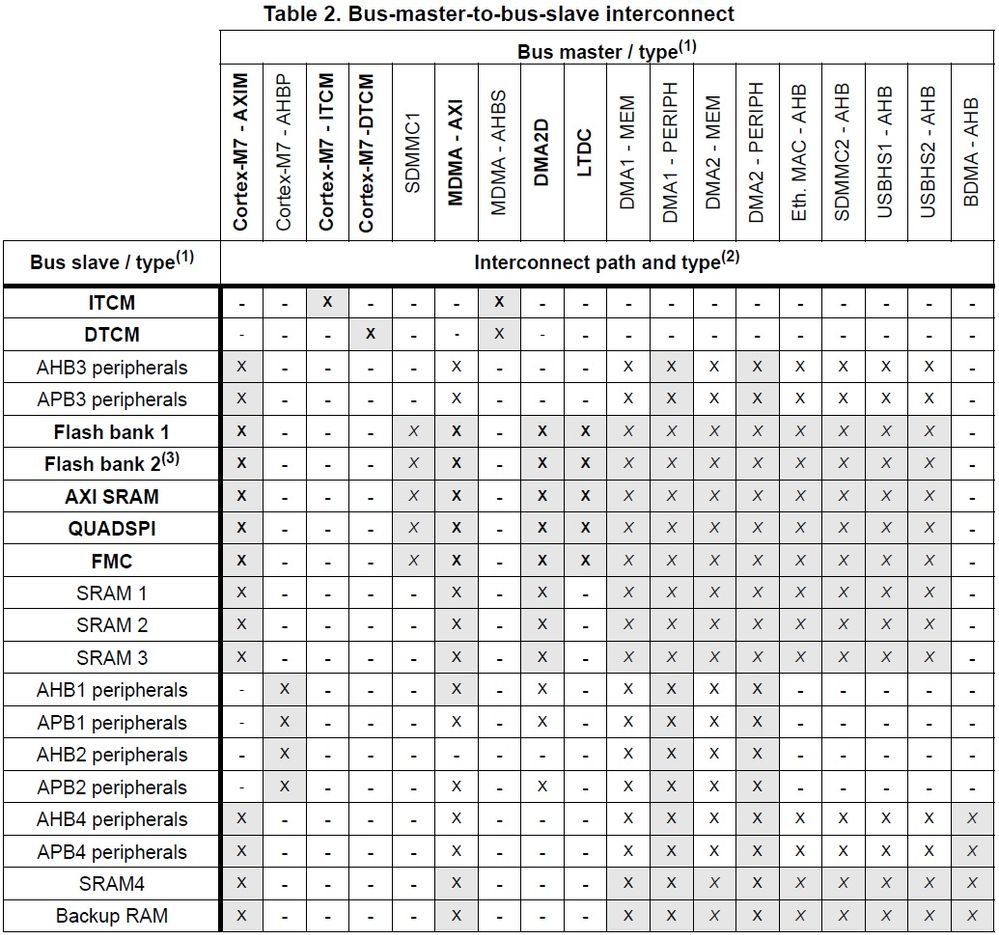

According to the bus matrix/routing diagrams DMA1 can't access DTCMRAM, and thus the error

Suggest using 0x24000000 AXISRAM or 0x30000000 (SRAM1,2,3)

You might also want to configure the MPU related to write-thru and caching, or manage the cache more directly to address coherency issues.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-13 1:22 PM

What is the address of the memory buffer?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-13 2:17 PM

Hi, the address is 0x20000040

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-13 2:49 PM

According to the bus matrix/routing diagrams DMA1 can't access DTCMRAM, and thus the error

Suggest using 0x24000000 AXISRAM or 0x30000000 (SRAM1,2,3)

You might also want to configure the MPU related to write-thru and caching, or manage the cache more directly to address coherency issues.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-13 3:31 PM

Thank you so much for your help! Now I see where the problem lies.

I did try ALIGN_32BYTES(__attribute__((section(".RAM_D2"))) uint32_t buff[512]) to put the buffer in somewhere other than DTCMRAM, but I just realized the address is 0x20000020 in this case, which is odd because RAM_D2 is 0x30000000 in the linker script.

Would you mind providing a example to show how to make it right?

Many thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-14 11:58 AM

Thanks for the help! Problem solved. I found the FAQ about DMA very helpful regarding this problem.

https://st-microelectronics.jiveon.com/docs/DOC-1988-faq-dma-is-not-working-stm32h7-devices