- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Capture Compare basic question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Capture Compare basic question

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-07 02:33 AM

Hi Everybody,

I have a problem understanding the capture compare functionality.I want to use channel1 to fire an interrupt if a match between CCR and counter is detected. In this case, CCR1 is set to 0xFFF+1. So the interrupt should never rise, because the counter restarts at 0xFFF this works fine for the TIM_OCMode_Toggle initialized on Channel3. Why is the TIM_IT_CC1 interrupt raised each counter overflow?

http://guyvo-cortex.blogspot.de/2009/04/pulse-timers.html this guy describes how it works, but why do the interrupt rises when the pulse is higher than the counter counts?Can someone help me understanding this?

By the way, I'm using an STM32F4void

TIM_test(

void

)

{

TIM_TimeBaseInitTypeDef TIM_TimeBaseStructure;

TIM_OCInitTypeDef TIM_OCInitStructure;

TIM_DeInit( TIM4 );

TIM_TimeBaseStructInit( &TIM_TimeBaseStructure );

TIM_TimeBaseStructure.TIM_Period =0xFFF;

TIM_TimeBaseStructure.TIM_Prescaler = 10000;

//((Prescaler/2)-1);

TIM_TimeBaseStructure.TIM_ClockDivision = 0;

TIM_TimeBaseStructure.TIM_CounterMode = TIM_CounterMode_Up;

TIM_TimeBaseInit(TIM4, &TIM_TimeBaseStructure);

TIM_OCStructInit( &TIM_OCInitStructure );

TIM_OCInitStructure.TIM_OCMode =TIM_OCMode_Toggle;

TIM_OCInitStructure.TIM_Pulse = 0xFFF+1;

//When a match is found between the capture/compare register and the counter

TIM_OCInitStructure.TIM_OutputState = TIM_OutputState_Enable;

TIM_OCInitStructure.TIM_OCPolarity = TIM_OCPolarity_High;

TIM_OCInitStructure.TIM_OCIdleState = TIM_OCIdleState_Reset;

TIM_OC3Init(TIM4, &TIM_OCInitStructure);

TIM_OCStructInit( &TIM_OCInitStructure );

TIM_OCInitStructure.TIM_OCMode = TIM_OCMode_Toggle;

TIM_OCInitStructure.TIM_Pulse = 0xFFF+1;

TIM_OCInitStructure.TIM_OutputState = TIM_OutputState_Enable;

TIM_OCInitStructure.TIM_OCPolarity = TIM_OCPolarity_High;

TIM_OCInitStructure.TIM_OCIdleState = TIM_OCIdleState_Reset;

TIM_OC1Init(TIM4, &TIM_OCInitStructure);

TIM_ITConfig(TIM4,TIM_IT_CC1,ENABLE);

TIM_Cmd(TIM4, ENABLE);

}- Labels:

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-07 04:21 AM

Hi

''I have a problem understanding the capture compare functionality.'' Everybody does - its complicated. ''I want to use channel1 to fire an interrupt if a match between CCR and counter is detected. In this case, CCR1 is set to 0xFFF+1.

'' ''http://guyvo-cortex.blogspot.de/2009/04/pulse-timers.html

this guy describes how it work'' ''TIM_TimeBaseStructure.TIM_Prescaler = 10000;

//((Prescaler/2)-1);

TIM_TimeBaseStructure.TIM_ClockDivision = 0;- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-07 04:34 AM

Of course I know the prescaler is very high

I want to visualize the problem using an LED!So again:

Actually I just want to raise an interrupt if there is a match between counter a CCR. This works. When I use half the value of the counter ARR-register, the interrupt is raised on this value.

In the datasheet I read:

When a match is found between the capture/compare register and the counter, the output

compare function: - Generates an interrupt if the corresponding interrupt mask is set (CCXIE bit in the

TIMx_DIER register).

So if the CCR is higher than the counter ARR there should be no interrupt. But there is on? Why? Can I disable it?

CLIVE1 where are you

J

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-07 04:48 AM

Hi

''So if the CCR is higher than the counter ARR there should be no interrupt. But there is on? Why? Can I disable it?

'' Which event is causing the IRQ? Which bit is set in TIMx_SR? ''CLIVE1 where are you

J

'' If you do not want my help - OK- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-07 05:21 AM

Of coure I also want your help!

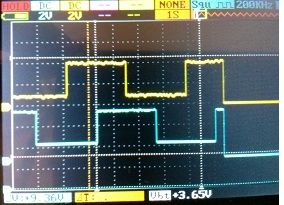

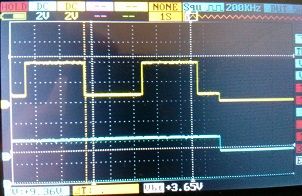

Here my Problem in pictures:

void

TIM_test(

void

)

{

TIM_TimeBaseInitTypeDef TIM_TimeBaseStructure;

TIM_OCInitTypeDef TIM_OCInitStructure;

TIM_DeInit( TIM4 );

TIM_TimeBaseStructInit( &TIM_TimeBaseStructure );

TIM_TimeBaseStructure.TIM_Period =20000;

TIM_TimeBaseStructure.TIM_Prescaler = 10000;

TIM_TimeBaseStructure.TIM_ClockDivision = 0;

TIM_TimeBaseStructure.TIM_CounterMode = TIM_CounterMode_Up;

TIM_TimeBaseInit(TIM4, &TIM_TimeBaseStructure);

TIM_OCStructInit( &TIM_OCInitStructure );

TIM_OCInitStructure.TIM_OCMode =TIM_OCMode_Toggle;

TIM_OCInitStructure.TIM_Pulse = 20000;

//When a match is found between the capture/compare register and the counter

TIM_OCInitStructure.TIM_OutputState = TIM_OutputState_Enable;

TIM_OCInitStructure.TIM_OCPolarity = TIM_OCPolarity_High;

TIM_OCInitStructure.TIM_OCIdleState = TIM_OCIdleState_Reset;

TIM_OC3Init(TIM4, &TIM_OCInitStructure);

TIM_OCStructInit( &TIM_OCInitStructure );

TIM_OCInitStructure.TIM_OCMode = TIM_OCMode_Inactive;

TIM_OCInitStructure.TIM_Pulse = 20000+1;

TIM_OCInitStructure.TIM_OutputState = TIM_OutputState_Enable;

TIM_OCInitStructure.TIM_OCPolarity = TIM_OCPolarity_High;

TIM_OCInitStructure.TIM_OCIdleState = TIM_OCIdleState_Reset;

TIM_OC1Init(TIM4, &TIM_OCInitStructure);

TIM_ITConfig(TIM4,TIM_IT_CC1,ENABLE);

TIM_Cmd(TIM4, ENABLE);

}CH1_Pulse = 20000

CH3_Pulse = 20000

CH1_Pulse = 10000

CH3_Pulse = 20000

CH1_Pulse = 20000

CH3_Pulse = 20000+1

CH1_Pulse = 20000+1

CH3_Pulse = 20000

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-07 05:24 AM

This is a feature (*).

RM0090 rev.5 p.619, ch.18.4.5 - description of TIMx_SR.CC1IF: When the contents of TIMx_CCR1 are greater than the contents of TIMx_ARR, the CC1IF bit goes high on the counter overflow (in upcounting and up/down-counting modes) or underflow (in downcounting mode) JW (*) if (Surprising()) { if (Documented()) { IsAFeature(); }else { IsABug(); }- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-02-07 05:31 AM

Thanks

waclawek.jan

, this is the answer I was searching for, but not the one I was hoping for!this do not make any sense! If I want to have this interrupt I can use TIM4_UPDATE!Edit: This is new with cortex M4 in Cortex M3 reference manual the world was still in order!- ADC module issues in STM32F429 in STM32 MCUs Boards and hardware tools

- STM32G0B1RE Using a timer to sample a clock signal in STM32 MCUs Products

- STM32H743VIT6 DCMI & JPEG encoder data validation interfacing with MT9M114 sensor. in STM32 MCUs Products

- 9 channels ADC to with DMA, Injected mode and interrupt mode in STM32 MCUs Embedded software

- MDMA Transfer in STM32 MCUs Products