- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: STM32F417IG single ended external clock bypass

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F417IG single ended external clock bypass

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-26 12:01 PM

Hi,

I am looking for some info regarding the external clock bypass conditions for STM32F417IG. There was not sufficient info in the datasheet. But, in the reference manual I could find some related data regarding how it can be done. Another problem was the Clock Config tool does not support the external clock bypass conditions. So, that was a problem in generating the required related C code to dump. I just wanted to confirm if the following changes in the system_stm32f4xx.h header file would be sufficient to use the chip in bypass conditions by feeding it using an external single ended clock source and have it communicating with the computer with VCP: I set it to pll_source_hse_bypass. and RCC->CR |= ((uint32_t)(RCC_CR_HSEON | RCC_CR_HSEBYP)); RCC->CR |= ((uint32_t)RCC_CR_HSEON); In the main.c: I have the following config- &sharpdefine HSE_VALUE((uint 32_t)8000000) should I leave it as it is or make any changes to this in main? I request you to please provide any other samples/code/reference design if available about the same conditions. I already tried with the modifications mentioned above and I think I partially bricked one of the device. I am able to program the flash but it is not able to communicate with pc as the VCP is not being detected. I thereby request you to please look into this and provide some solutuon. Thanks, Sa #stm32f417 #stm32f417 #stm32f417 #hse-hsi-pll-rcc #vcp-stm32f4 #rtfm #external-clock #hse-config- Labels:

-

STM32F4 Series

-

USB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-26 05:36 PM

One wonders how we ever survived before someone created an Excel sheet....

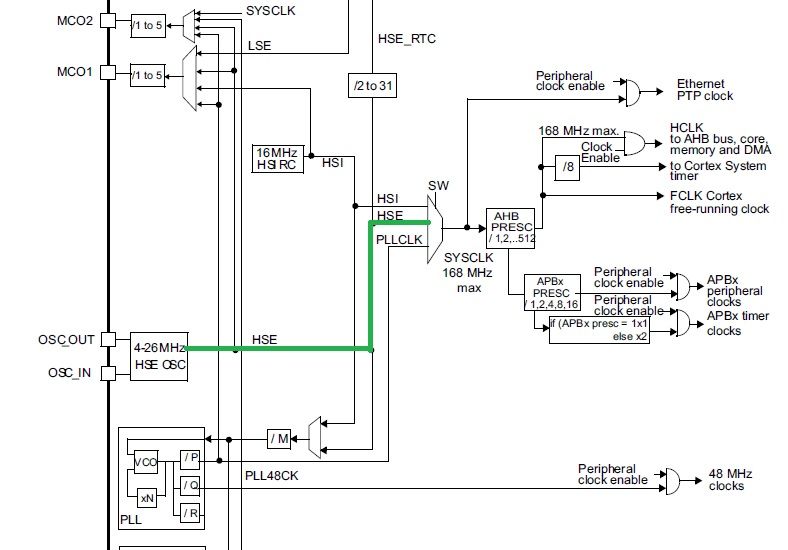

The HSE_VALUE need to reflect the frequency of the external source, whatever that is. The Q Tap of the PLL needs to be 48 MHz, and the PLL needs to be locked and clocking for USB to function. If you wish to confirm the internal clocks they can be routed out MCO1 (PA8)Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-26 05:48 PM

Thanks for reply clive1.

I will set the HSE_VALUE to whatever frequency I am feeding it via the externally generated clock andfor the USB VCP comm I will set the following-#define PLL_Q 48

Should I set the pll_source_hse_bypass macro or should it be either of#define PLL_SOURCE_HSI

#define PLL_SOURCE_HSE

Please correct if I am wrong.- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-27 03:32 AM

Ok, let's try this

What frequency is your external clock? What speed do you want the processor to run at? What are the current PLL settings? Yeah, I don't think ''#define PLL_Q 48'' is valid, it's a divisor from the PLL clock, which isn't capable of 2.3 GHz The source is EXTERNAL, the BYPASS setting means it's not driving the OUT pin for an external crystal. You will be driving the PLL with the HSE.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-27 08:03 AM

What frequency is your external clock?

I want to run it at 270 Mhz(external single ended clock fed through PH0). What speed do you want the processor to run at? The processor to be run at the same speed as the external clock(=270). What are the current PLL settings? Current PLL settings: Uncommented -#define PLL_SOURCE_HSE_BYPASS, then following flags have been set.

RCC->CR |= ((uint32_t)(RCC_CR_HSEON | RCC_CR_HSEBYP));

RCC->CR |= ((uint32_t)RCC_CR_HSEON);Did not change default value of

#define PLL_Q . Please correct if wrong. Thanks- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-27 09:19 AM

Ok, but the CPU isn't rated for that speed, and fHSE_ext is specified to support 1 to 50 MHz?

The PLL will clock at 270 MHz with a non 50/50 duty allowing the processor to run at 135 MHz. Also 270 MHz is NOT divisible by 48, so USB probably not going to work absent an external PHY. You might want to review the Data Sheet for your part.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-27 10:24 AM

I have made the following hardware mods to send in the externally generated clock -

• cut between OSC_IN (where we give our clock) and the resistor, add a microwire to the resistor side so we can connect it back • Solder a thin wire to the resistor pad and connect it to the GPIO pin PH0The above procedure is as mentioned in the reference manual -

In this mode, an external clock source must be provided. You select this mode by setting the HSEBYP and HSEONbits in the RCC clock control

register (RCC_CR)HSEBYP and HSEON bits in the RCC_CR. The external clock signal (square, sinus or triangle) with ~50% duty cycle has to

drive the OSC_IN pin while the OSC_OUT pin should be left HI-Z. See Figure 17.signal (square, sinus or triangle) with ~50% dusignal

(square, sinus or triangle) with ~50% duty cycle has to drive the OSC_IN pin while the OSC_OUT pin should be left HI-Z.

I will drop the clock freq to 192 which is a multiple of 48. Could you please tell if these settings would need any other software changes?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-27 10:33 AM

HSE clock at OSC_IN : 1 MHz to 50 MHz

CPU speed up to 168 MHzUp vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-27 11:11 AM

Clive,

Is there anyway to bypass the PLL? Because that is the limiter on 50 MHz. Else even high frequencies can be fed externally?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-10-27 11:20 AM

Look you can select HSE as a direct source to clock the processor. The oscillator is specified from 4 to 26 MHz, the external source from 1 to 50 MHz, outside that you're in uncharted territory. USB and SDIO require the PLL

Up vote any posts that you find helpful, it shows what's working..

- H7RS HSE Analog Bypass Oscillators in STM32 MCUs Products

- 2500 W motor control power board based on STGIB30M60TS-L SLIMM™ 2nd serie IPM in STM32 MCUs Motor control

- Clarification on STM32H7A3 Power Supply Configuration with LQFP64 Package in STM32 MCUs Products

- Comparing the memory map between RM and CubeMX linker file; what's up with the differences? in STM32CubeMX (MCUs)

- What is the correct connection for VCAP1 and VCAP2? in STM32 MCUs Products