- STMicroelectronics Community

- Product forums

- Power management

- Cost-efficient remote reset of STPM3x

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Cost-efficient remote reset of STPM3x

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 8:40 AM

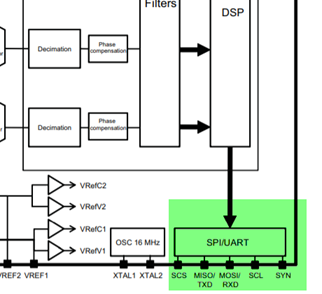

STPM32 is used for an e-meter application. Idea is to use 2-pin UART connection, isolate only the RX and TX with optocouplers and not to use the SYN and SCS for reset.

According to datasheet on page 68 the remote reset can be performed in two ways:

· Using SYN and SCS pin

· Writing the reset bit (S/W reset in DSP_CR3)

Does this last option correctly reset the chip, especially the DSP unit? In this case, two optocouplers would not be needed for the SYN and SCS lines. Will it work as expected ?

NOTE: This question and answer originated from a customer support case which was handled by us. We regularly review support cases and add any helpful ones here for all to benefit from.

Solved! Go to Solution.

- Labels:

-

Motor Control Hardware

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 8:43 AM

In fact, pulses on SYN and SCS are mandatory to correctly reset the chip set.

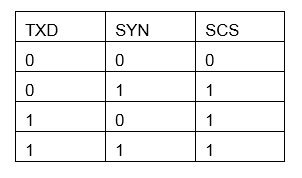

But in this specific case there is a way to save at least one optocoupler by generating SCS from SYN + TXD signals: you put an OR gate with SYN and TXD as inputs, and SCS as output (the OR gate can be replaced also by 2 diodes).

Resulting true table will be:

Then, at each power-on sequence:

· Send 3 pulses on SYN (TXD being high)

· Send 1 pulse on SCS with SYN/TXD combination

In the example code below, I set SYN to "0", then send 0x00 on TXD, wait a delay, finally set back SYN to "1".

GPIO_ResetBits( GPIO9, SYN_STPM32);

USART_SendData(USART3,0x00);

INIT_WaitMicroSecond(10000);

GPIO_SetBits( GPIO9, SYN_STPM32);Note: Be sure that at power-on (when EN and 3.3V rise), SCS signal must be high to lock the chipset in UART mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-27 8:43 AM

In fact, pulses on SYN and SCS are mandatory to correctly reset the chip set.

But in this specific case there is a way to save at least one optocoupler by generating SCS from SYN + TXD signals: you put an OR gate with SYN and TXD as inputs, and SCS as output (the OR gate can be replaced also by 2 diodes).

Resulting true table will be:

Then, at each power-on sequence:

· Send 3 pulses on SYN (TXD being high)

· Send 1 pulse on SCS with SYN/TXD combination

In the example code below, I set SYN to "0", then send 0x00 on TXD, wait a delay, finally set back SYN to "1".

GPIO_ResetBits( GPIO9, SYN_STPM32);

USART_SendData(USART3,0x00);

INIT_WaitMicroSecond(10000);

GPIO_SetBits( GPIO9, SYN_STPM32);Note: Be sure that at power-on (when EN and 3.3V rise), SCS signal must be high to lock the chipset in UART mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 3:50 AM

And what about SPI communication please ? i can't ensure it ? can you help me ?

- STPM3x Calibration Setup Understanding in Power management

- Unable to upload code via st link v2 on stm32h725vgt6 in STM32CubeIDE (MCUs)

- StmCube IDE Remote debugging issue in STM32CubeIDE (MCUs)

- STSAFE-A110 Data encryption/decryption using secret key in Others: STM32 MCUs related

- BLE Mesh: Proxy node doesn't relay application messages via advertising bearer in STM32 MCUs Wireless