- STMicroelectronics Community

- Product forums

- STM8 MCUs

- TIM1 registers read errata

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TIM1 registers read errata

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-09 1:00 AM

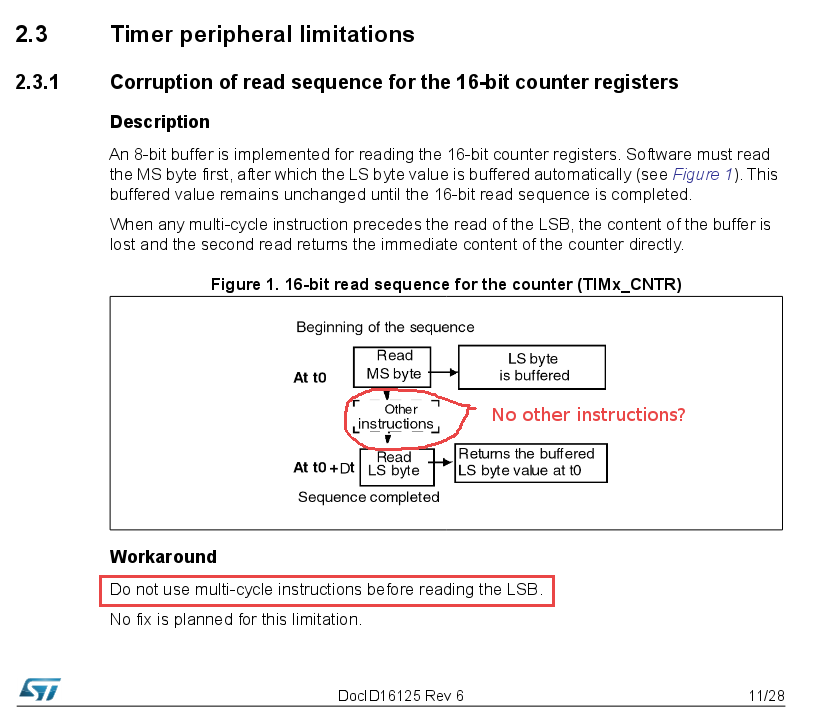

So, info in reference manual is irrelevant? The read should be always done as:

; Read Seq_1

ld A, TIM1_REGH;

ld XL, TIM1_REGL;�?�?�??

Will the following sequences lead to incorrect results?

; Read Seq_2

ldw X, #TIM1_REGH; Store in X address of TIM1_REGH

ld A,(X); Read TIM1_REGH

push A;

incw X; Set pointer to TIM1_REGL

ld A,(X); Read TIM1_REGH�?�?�?�?�?�?

; Read Seq_3

ldw X, #TIM1_REGH; Store in X address of TIM1_REGH

ld A,(X); Read TIM1_REGH

push A;

ldw X, #TIM1_REGL; Store in X address of TIM1_REGL

ld A,(X); Read TIM1_REGL�?�?�?�?�?�?�?�?

�?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-19 1:42 AM

Hello,

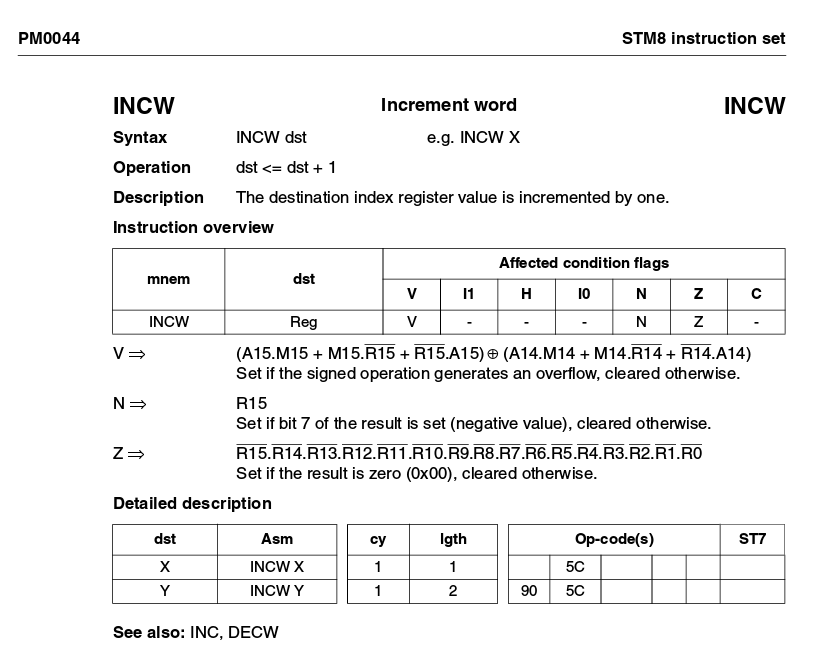

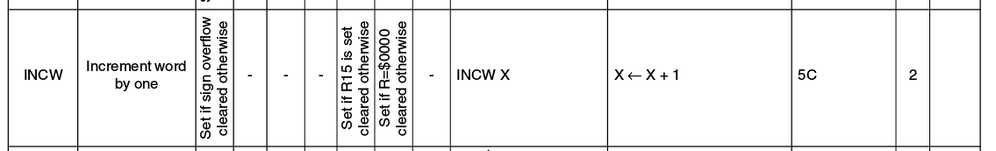

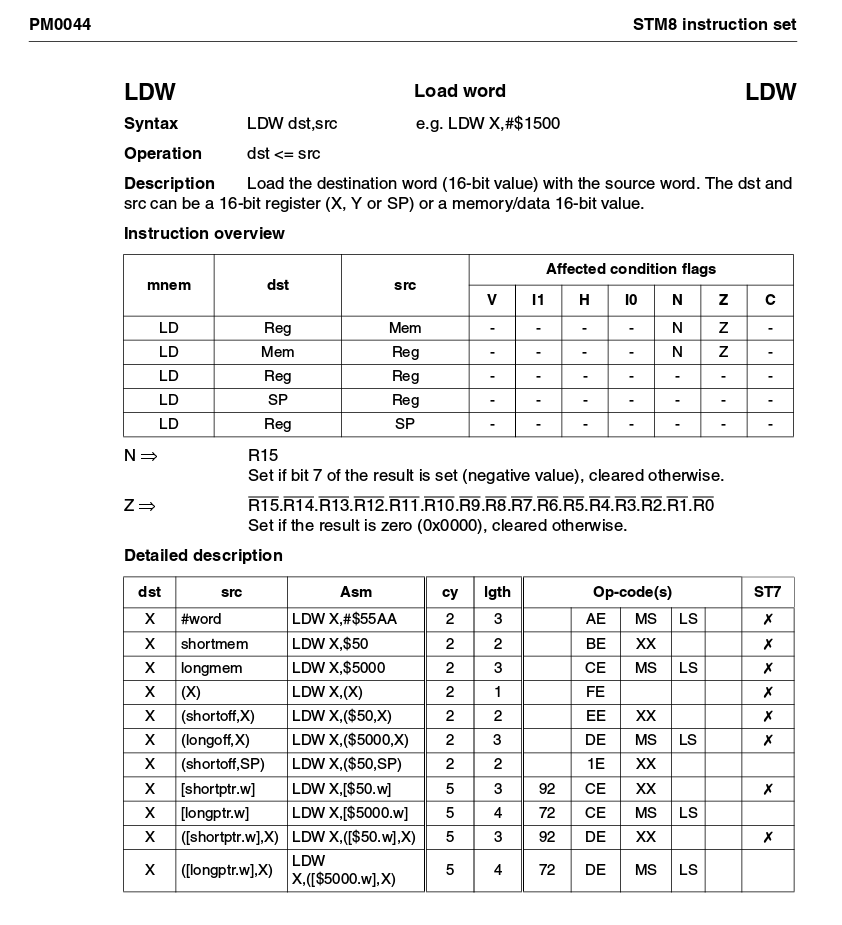

In the three code snippets you are referring too, the only multiple cycle instruction is the INCW X you have in the Read seq_2

As a consequence Read seq_1 and Read seq_3 are OK, but you should not use Read seq_2 for 16-bit TIMer access.

This also means that the recommendation in the RM is correct.

If you want to check if an instruction execute in multiple cycles, please refer to

.The Table 42 page 64 to 74 has a column showing the number of cycles.

Let me know if this is still not clear

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-19 3:24 AM

This is from doc linked by you:

1 cycle or 2? Where the truth?

And for Seq_3: ldw is 2 cycle instruction. It's used to load TIM1->CNTRL to index register.

in Seq_1 I've made mistake. LD could not load from memory to XL.

So, none of this three reads will assemble or return correct result.

Currently I'm using ''mov _store_mem, _read_mem

mov _cnt_hi, TIM1_CNTRH

mov _cc_hi, TIM2_CCR1H

mov _cnt_low, TIM1_CNTRL

mov _cc_low, TIM2_CCR1L�?�?�?�?Does it get the job? Because I don't know how peripheral feature could be impacted by instruction size or exec time. And what if I have 5-10-20 single cycle instructions between reading High and Low registers?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-19 5:19 AM

I tried it out on a STM8S103F3P6 rev Y, and no matter what I do, I cannot get the timer read to return the wrong answer, as long as I read TIM1_CNTRH before TIM1_CNTRL. I even tried reading CNTRH, calling a function to write that value to the UART, reading CNTRL, and it was still correct.

My test procedure: stop counter, write 0xffxx to CNTR, start counter, handful of NOPs, and then read CNTRH/CNTRL in various ways. Repeat with incrementing start value. At some point, you'll see the timer roll over.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-07-15 5:24 PM

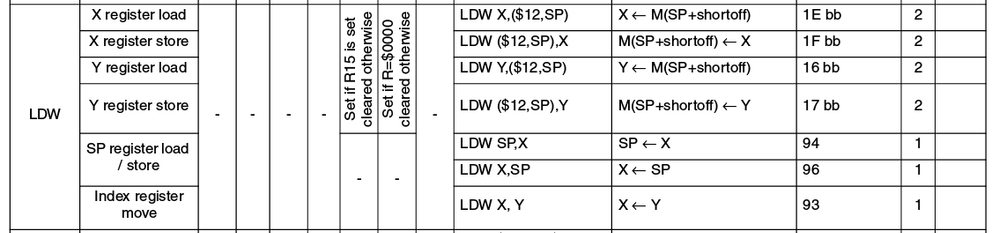

Is it not advisable to load both registers using ldw ?

Like this:

uint16_t tim3_last = *(const uint16_t *)&(TIM3->CNTRH);

which produces:

ldw x, 0x5328

ldw (0x07, sp), x

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-07-16 5:03 AM

RM0016 page 142: Do not use the LDW instruction to read the 16-bit counter. It reads the LS byte first and returns an incorrect result.

- STM32N6570-DK LRUN project does not boot in STM32 MCUs Boards and hardware tools

- "Error in final launch sequence" with Cube IDE 2.0.0 and J-Link Plus in STM32CubeIDE (MCUs)

- STM32H7RS SWR-Bit wont clear; LWIP + FreeRTOS in STM32 MCUs Embedded software

- TSC1641 The values of the current and power registers appear to be swapped. in Others: hardware and software

- [STM32G0B0] External interrupt in STM32 MCUs Products