- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Wireless

- STM32WB55 RTC with battery backup

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32WB55 RTC with battery backup

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-29 9:51 AM

Hello everyone, I hope you are well.

I'm working with the STM32WB55. I'm having difficulty getting RTC to work correctly.

The VBat is always powered by 3v3, I have an on/off switch that only removes the power from the VDD, however, when I turn it off and on the microcontroller is stuck in the routine: "while (LL_RCC_LSE_IsReady() == 0U)". I noticed that when CFG_HW_RESET_BY_FW is 1, the board continues to function, but it resets the RTC registers and the time is lost and when CFG_HW_RESET_BY_FW = 0, the firmware is stuck in the "while (LL_RCC_LSE_IsReady() == 0U)" routine. Looking through the oscilloscope, the clock is all right.

Can anyone help me? Thank you very much!

Solved! Go to Solution.

- Labels:

-

BLE

-

STM32WB series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-07 4:25 AM - edited 2024-02-07 4:27 AM

Hello @ffjunq,

- Are you waking up from any low power modes ? Can you share your code and the LSE config ?

- I saw on your screen that LSECSSD is equal to 0x1. It means a failure is detected on LSE (32 kHz oscillator) by the CSS. Have you try with the LSI clock ?

- Also, Have you respected the sequence ?

- First enable LSE oscillator with LSEON

- Then, wait the ready flag LSERDY (set by hardware)

- And select the clock source with RTCSEL (= 0x1 for LSE)

- Finally, enable LSECSSON. (Once enabled LSECSSON cannot be disabled, except after a LSE failure detection (LSECSSD = 1). In that case the software MUST disable the LSECSSON bit.)

- Yes, as long as the supply voltage remains in the operating range, the RTC never stops, regardless of the device status (Run mode, low-power mode or under reset).

- For the supercap, are you aware of the AN4718 ?

- Unfortunately, I just checked ES0394 and the issue is mentionned (it's n° 2.2.2 : Unstable LSI1 when it clocks RTC or CSS on LSE) You need to apply one of the following measures :

- Clock the RTC with LSE or HSE/32, without using the CSS on LSE.

- If LSI1 clocks the RTC or when the LSECSSON bit is set, reset the backup domain upon each VDD power

up (when the BORRSTF flag is set). If VBAT is separate from VDD, also restore the RTC configuration,

backup registers and anti-tampering configuration.

- Also, are you using PC13 in your application ? (I am referring to issue 2.2.6 : PC13 signal transitions disturb LSE)

- Can you confirm this is the problem (VBAT is separate from VDD and VDD goes off then on) ? And can you please try the workaround and let me know ?

Kind Regards,

Pierre

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-06 2:33 AM

Hello @ffjunq,

Thank you for your question !

Here some remarks :

- Can you explain your application ? Why are you always powered by 3.3v ? Are you trying to generate an internal timestamp when a switch to Vbat occurs ?

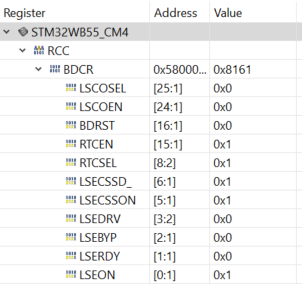

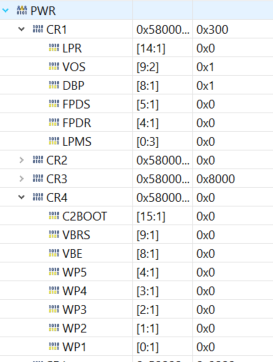

- When you are stuck in the while, can you share the value of PWR_CR1, PWR_CR4, RCC_BDCR (especially LSEON, LSEBYP bits) ?

- VBAT operation is automatically activated when VDD is not present. An internal VBAT battery charging circuit is embedded and can be activated when VDD is present.

- When CFG_HW_RESET_BY_FW is equal to

- 0 : No reset.

- 1 : It resets the Backup domain, that's why you are loosing the time. A backup domain reset only affects the LSE oscillator, the RTC, the Backup registers and the RCC Backup domain control register.

- Are you using the CSS on LSE ? Are you monitoring Vbat with the ADC ?

- Have you read chapter 6.1.4 Battery backup domain in RM0434 ?

Best Regards,

Pierre

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-06 5:42 AM

Hi Pierre, thank you very much for your support.

- I need to make my RTC never reset, so the VBAT is always in 3v3, remembering that I am using a V3 stlink to power the circuit. I have an on/off switch that only interferes with VDD, that is, VBat always 3v3.

- Following are the values of the registers:

- I don't need to charge the battery using VBat, as in the hardware I will use a specific chip to do this.

- In this case, I understand that the CFG_HW_RESET_BY_FW for my application always needs to be 0, so that it does not reset my RTC.

- Yes, I'm using CSS, but I've already tested with CSS off. And I'm not monitoring the VBat with the ADC, because I don't see the need for it at the moment, it may be that in the future I can use it to read the battery level, but I would have to check the possibility, since my battery is 4.2 V to 3V

- Yes, I have already read this document. However, I am performing again.

Thank you very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-06 10:30 AM

Taking advantage, I would like to know if there is a schematic of the ST, using a super capacitor so that the VBat is always at 3v3.

Thanks in advance!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-07 4:25 AM - edited 2024-02-07 4:27 AM

Hello @ffjunq,

- Are you waking up from any low power modes ? Can you share your code and the LSE config ?

- I saw on your screen that LSECSSD is equal to 0x1. It means a failure is detected on LSE (32 kHz oscillator) by the CSS. Have you try with the LSI clock ?

- Also, Have you respected the sequence ?

- First enable LSE oscillator with LSEON

- Then, wait the ready flag LSERDY (set by hardware)

- And select the clock source with RTCSEL (= 0x1 for LSE)

- Finally, enable LSECSSON. (Once enabled LSECSSON cannot be disabled, except after a LSE failure detection (LSECSSD = 1). In that case the software MUST disable the LSECSSON bit.)

- Yes, as long as the supply voltage remains in the operating range, the RTC never stops, regardless of the device status (Run mode, low-power mode or under reset).

- For the supercap, are you aware of the AN4718 ?

- Unfortunately, I just checked ES0394 and the issue is mentionned (it's n° 2.2.2 : Unstable LSI1 when it clocks RTC or CSS on LSE) You need to apply one of the following measures :

- Clock the RTC with LSE or HSE/32, without using the CSS on LSE.

- If LSI1 clocks the RTC or when the LSECSSON bit is set, reset the backup domain upon each VDD power

up (when the BORRSTF flag is set). If VBAT is separate from VDD, also restore the RTC configuration,

backup registers and anti-tampering configuration.

- Also, are you using PC13 in your application ? (I am referring to issue 2.2.6 : PC13 signal transitions disturb LSE)

- Can you confirm this is the problem (VBAT is separate from VDD and VDD goes off then on) ? And can you please try the workaround and let me know ?

Kind Regards,

Pierre

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Keep RTC active when STM32WBA65RIV6 is powered down in STM32 MCUs Wireless

- In Shutdown, how is RTC powered? in STM32 MCUs Products

- STM32U535CCT6 Trustzone non-secure is inflashable in STM32 MCUs Security

- How to backup/restore value of variables in STM32N6570-DK board in STM32 MCUs Products

- TouchGFX project: FreeRTOS or ThreadX available, but not AzureRTOS ? in STM32 MCUs TouchGFX and GUI