- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs TouchGFX and GUI

- Re: Hi I'm using STM32H743 nucleo 144 with ltdc co...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Hi I'm using STM32H743 nucleo 144 with ltdc configurations and I'm using internal clock. The program stacks in ltdc init() in lines that initialize GCR register. What can be the problem?

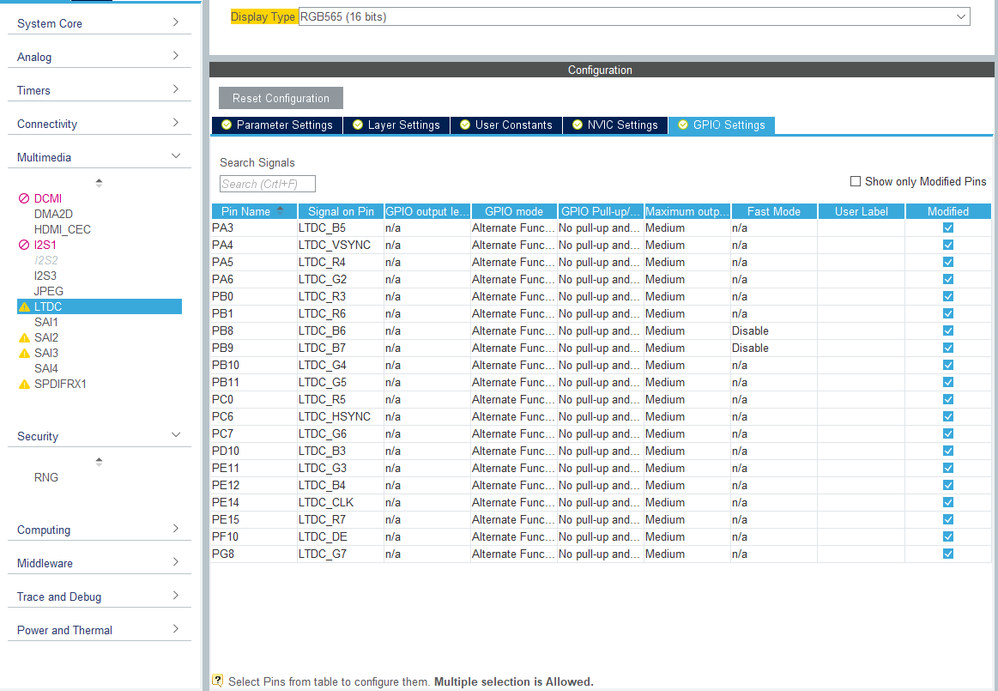

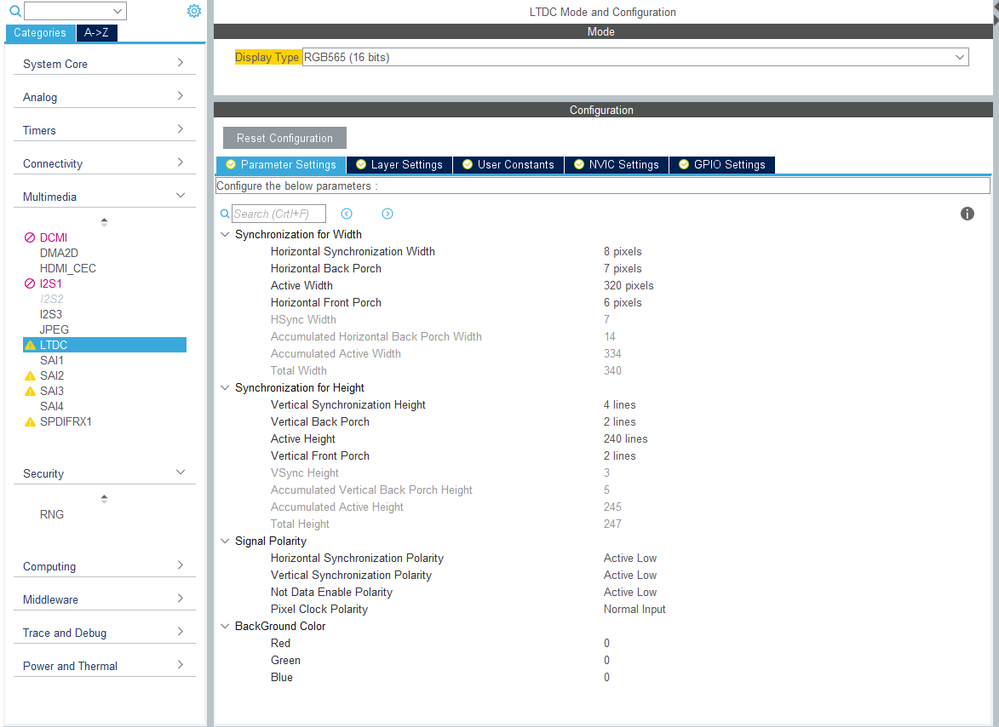

Below are some configuration of ltdc

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-07-03 01:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-10 01:34 PM

Hi yshnaider, how did you solve the Issue? I’m having the same problem now.

I used the LTDC module many times on the STM32F429 without problem but the STM32H743 seems to be different on it.

The revision code of my device is “V�?, in the errata manual ST suggest to enable the pixel clock before write the CGR register, but CubeMX and HAL drivers Seem to do this operation already.

I don’t know how to solve this issue.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-17 11:57 PM

Hi everyone

I also have the same problem.

I asked you have STM technicians, let's see what they tell me.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-18 06:14 AM

Hi all,

as I posted in another discussion, I write my experience and I hope it can helps someone :)

I solved this issue in my embedded board.

The problem, in my case, seems to be caused by a CubeMX bug.

The VCO Range of the PLL3 (the one used to generate the pixel clock of the LTDC module) cannot be selected in MEDIUM mode but only WIDE.

If one of the PLL outputs (P, Q, R) have a frequency higher than 192MHz there are no problems, otherwise the microcontroller will stall during the initialisation phase of the LTDC module because the pixel clock is not active.

It is possible to solve the problem in two ways, the first one is to set one of the three outputs, if not used (P, Q or R) with a clock at 200MHz for example, the other solution is to manually modify the PeriphClkInitStruct.PLL3 parameter. PLL3VCOSEL from RCC_PLL3VCOWIDE to RCC_PLL3VCOMEDIUM.

In this case, however, every time a change is made to the project on CubeMX, the parameter returns to the wrong value.

Gianluca

- CubeMX and CubeIDE interaction - User Code being overwritten in STM32 MCUs Products

- STM32WB55CGU7 - Need BLE configuration for upto 10m distance in STM32 MCUs Wireless

- LL_SPI_SetMode to configure SPI2_CFG2 Master bit not working reliably? in STM32 MCUs Embedded software

- Join Request approved by gateway but not received by device in STM32 MCUs Wireless

- STL v4.0.0. : Flash test not passed + bin file size is 393MB in STM32 MCUs Products