- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: What is the best way to use the serial device ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What is the best way to use the serial device in this case?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-23 9:08 AM

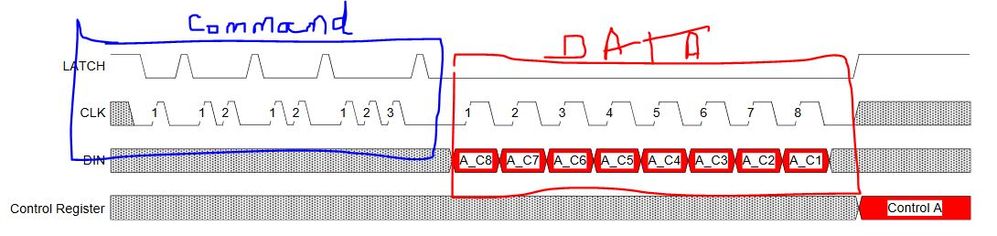

I am currently using a driver that uses latch and clock signals to send special commands before sending data.

For the sending of the data the driver works as for an SPI but with the signal of clock.

Here is the diagram.

To interact with this driver I am currently using the microcontroller pins in GPIO out and I generate the output signals without using the SPI device.

The problem is that by doing this I block my application while if I used the device SPI I could do something else in parallel.

Because if I want to use my SPI port I will have to whenever I want to sent the start of the special command reconfigure the pins out and once the special command sent reconfigure the device SPI.

Is there a way to manage this kind of communication?

Thanks in advance !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-23 10:14 AM

There are always ways to do it. Two from me.

1. Rewrite your subroutine via interrupt. The easiest.

2. Rewrite an interrupt based routine for your own transmission. Not too difficult.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-24 12:32 PM

Could perhaps use DMA+TIM to send a pattern buffer to GPIOx->BSRR

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-24 12:55 PM

Hello and thank you for your answer dhenry.

I do not really understand the difference between your two proposals but I know that I can use the interrupts to manage this

What I would like to know is if between the COMMAND part and the DATA part I have to change the alternate function of the pin.

In part command I have to be in GPIO out configuration to send different clock and latch spikes and then reconfigure my pin for SPI function ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-24 2:41 PM

Thanks clive for your answer!

I had never heard that it is possible to make patterns of this kind.

I will inquire.

Thanks so much

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-24 3:09 PM

It is the automated version of manually bit-banging the GPIO pins to get the sequences you want. The TIM+DMA provides for a more consistent timing/pacing, and allows for very high speed with low CPU utilization.

Classical implementation of a multi-channel sequencer

https://www.youtube.com/watch?v=kACVLOcRidg

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-24 3:59 PM

thank you again for your answer.

Would you know an example delivered by ST that looks like what I want to do?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-24 5:32 PM

I've posted plenty of examples of this over the years, I think ST has an app note about such things these days.

Issues depend on processor in question, the F4 series need you to use DMA2 based on the bus plumbing, ie Memory-to-Memory, GPIO has to be treated like normal memory rather than expedited transfer on APB1/2 via DMA1/2 respectively.

Look for a TIM CHx/UP trigger related to specific DMA Channel/Stream

Up vote any posts that you find helpful, it shows what's working..

- "No device found on target" when trying to flash something with ST-Link V2. in STM32 MCUs Products

- Sending ADC data directly over UART via DMA in STM32 MCUs Products

- STM32wb55 does not show connected even if connected to the phone in STM32 MCUs Wireless

- I²C Bus Stuck Issue – STM32G0 Slave Holding SCL Low During Hot-Swapping in STM32 MCUs Products

- STM32H7RSxx OTG strange behavior with bulk transfer in STM32 MCUs Products