- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Using DMA from ADC to DTCM with STM32F765VITx

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Using DMA from ADC to DTCM with STM32F765VITx

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-30 2:52 PM

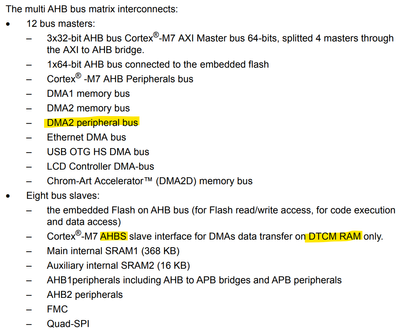

I have a project that is using DMA channels to transfer ADC values to DTCM. The values seem to be getting to the memory correctly but I was confused by Figure 1 of the datasheet which shows the ADC/DMA/SRAM on the AHB but the DTCM on a bus that appears to be disconnected from the AHB -> https://www.st.com/resource/en/reference_manual/rm0410-stm32f76xxx-and-stm32f77xxx-advanced-armbased-32bit-mcus-stmicroelectronics.pdf

What is the path the data is taking from the ADC to the DTCM? Is there any timing penalty from the data taking this path?

Solved! Go to Solution.

- Labels:

-

DMA

-

STM32F7 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-30 3:38 PM

The AHBS connects DTCM RAM to the bus matrix.

Not much is published on the speed of various transfers within the chip, but given that the AHBS is a slave just like interfaces to SRAM, the speed is likely comparable to what you'd get transferring it into SRAM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-30 3:38 PM

The AHBS connects DTCM RAM to the bus matrix.

Not much is published on the speed of various transfers within the chip, but given that the AHBS is a slave just like interfaces to SRAM, the speed is likely comparable to what you'd get transferring it into SRAM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-31 5:16 AM

Honestly, this morning I don't see how I missed that AHBS line connecting to DTCM through the Cortex-M7 last night. Thanks for the reply.