- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Timer update DMA generation problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Timer update DMA generation problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-07 7:30 AM

Hello! I'm working with stm32f042 MCU. My task is to read GPIO 8-bit data (7-0 bits) periodically, the faster, the better. I use timer 3 to generate DMA request and DMA channel 4. The idea is the following one: timer periodically generates DMA request on update event, so GPIO->IDR is read. But it doesn't work. Timer doesn't generate DMA request, DMA counter doesn't change, no GPIO reading happens.

Init code

//DMA channel 4

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-07 10:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-07 7:36 AM

Init code

//DMA channel 4

RCC->AHBENR |= RCC_AHBENR_DMAEN;

DMA1_Channel4->CPAR = (uint32_t) (&(GPIOA->IDR)); DMA1_Channel4->CMAR = (uint32_t)(GpioData); DMA1_Channel4->CNDTR = Size; DMA1_Channel4->CCR = DMA_CCR_MINC | DMA_CCR_TEIE | DMA_CCR_TCIE; DMA1_Channel4->CCR |= DMA_CCR_EN; NVIC_EnableIRQ(DMA1_Channel4_5_IRQn); NVIC_SetPriority(DMA1_Channel4_5_IRQn,0);//Timer 3

RCC->APB1ENR |= RCC_APB1ENR_TIM3EN;

//TIM3->CR2 |= TIM_CR2_MMS_1; //tried that, no results TIM3->DIER = TIM_DIER_UDE;//TIM3->DIER |= TIM_DIER_UIE | TIM_DIER_TDE ; //tried that, no results

TIM3->PSC = 47999; TIM3->ARR = 100; TIM3->CR1 |= TIM_CR1_CEN;What am I doing wrong?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-07 10:10 AM

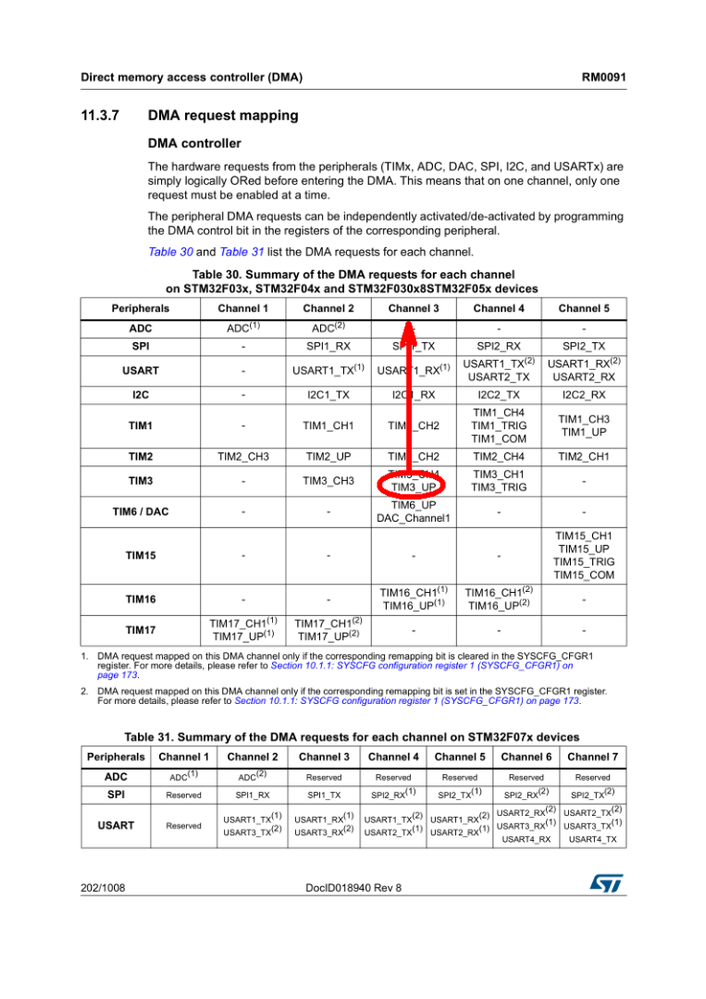

Incorrect DMA channel?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-07 2:04 PM

Thank you very much, waclawek.jan! That was it. I thought the source was TIM3_TRIG corresponding DMA channel 4.

By the way, what maximum data frequency can be achieved by using scheme 'timer-DMA-GPIO->IDR'?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-07 3:50 PM

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-07 5:06 PM

See AN2548 .

JW

- Authentication Error Manager :- myST account login failure in STM32CubeIDE (MCUs)

- generate multithread safe random generator (NX_RAND) for NetX Duo & newlib in STM32 MCUs Embedded software

- ADC DMA Buffers not Updating (multi-peripheral with timer trigger) in STM32 MCUs Embedded software

- H755: Need to erase full chip flash memory after every powerloss to the board in STM32 MCUs Boards and hardware tools

- LoRaWAN_End_Node_LBM v1.5.0, US915, B-WL5M-SUBG1, TX Power Too Low - with possible solution in STM32 MCUs Wireless