- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F746 Quad SPI in Legacy mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F746 Quad SPI in Legacy mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-18 3:52 AM

I'm working on project involving STM32F746 in QFP208 package.

Reference manual states that in Legacy SPI mode (which may be used for compatibility purposes) pins are configured as:

•

IO2 is in output mode and forced to ‘0’ (to deactivate the “write protect� function)

•

IO3 is in output mode and forced to ‘1’ (to deactivate the “hold� function)

But WRITE_PROTECT function on all chips I know (on test board will be SST25VF032B, final version will use W25Q128FV) is in negative logic, so to deactivate it we need to force '1' state on this lane, and not '0'. Am I wrong with my understanding of this situation?

And another question: I'lm planning to use pins PF6,7,8,9 for QUADSPI_BK1_IOx bus.

But here

I see that someone experienced problems with it.And I see advice 'QUADSPI_BK1_IO2 should be used for PE2 pin'. But why? Errata says nothing about this specific pin, so my question is: is it safe to use this pinout?#quad-spi #stm32f746- Labels:

-

QSPI

-

STM32F7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-27 2:23 AM

Hello

Solotchin.Eugene

,- I advise you to take a look at to have a deeper idea about the Quad-SPI interface on the STM32 microcontrollers.

- PE2 or PF7 could be used as 'QUADSPI_BK1_IO2' on the STM32F745xx and STM32F746xx devices.

However, if you are using a discovery board with an STM32F746NG MCU, then you have to use the pin PE2.

This pin is connected to the 'BK1_IO2' pin of the Quad-SPI memeory embedded on the discovery board.Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-27 9:12 AM

My board is not based on Discovery schematics, I'm free to choose any possible combination of IOs and PF6,7,8,9 looks pretty good. So if you say its okay, I'll fix this pinout in my design.

And yes, this

/external-link.jspa?url=http%3A%2F%2Fwww.st.com%2Fcontent%2Fccc%2Fresource%2Ftechnical%2Fdocument%2Fapplication_note%2Fgroup0%2Fb0%2F7e%2F46%2Fa8%2F5e%2Fc1%2F48%2F01%2FDM00227538%2Ffiles%2FDM002275pdf%2Fjcr%3Acontent%2Ftranslations%2Fen.DM002275pdf

is exactly what I'm reading.Quote follows:The IO2 and IO3 lines are optional and can be used for other purposes such as:

•

When used (IO2 and IO3 are connected to the QSPI memory): IO2 and IO3 pins

should be configured as for IO0 and IO1. To allow communication with memory device: – IO2 is in output mode and forced to ‘0’ to deactivate the “write protect�? function – IO3 is in output mode and forced to ‘1’ to deactivate the “hold�? function – This is managed by the hardware (Quad-SPI peripheral) during all communication phases•

When not used, the nWP and nHOLD memory device pins have to be connected

respectively to VDD and VSS while IO2 and IO3 pins could be used for other purposes.But when I'm reading datasheet for SPI flash (

SST25VF032B

for instance), I see this:The Write Protect (WP#) pin enables the lock-down function of the BPL bit (bit 7) in the status register.

When WP# is driven low, the execution of the Write-Status-Register (WRSR) instruction is determined by the value of the BPL bit (see Table 2). When WP# is high, the lock-down function of the BPL bit is disabled.I've checked few different chips from different vendors. Logic behind #WP is the same everywhere, and this is exactly what is confusing me: hardware in STM32 forcing this pin to '0' assuming that this will disable WriteProtect function, but in fact result is opposite and all writes to Status Register are blocked unless SR.BPL bit was previously cleared. Fortunately enough, in SST25 this bit (SR.BPL) is cleared on power up.

I guess, in case if legacy SPI flash is used, QSPI.IO2 pin should be configured as GPIO and forced to '1' or '0' when its really needed.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-27 9:13 AM

Hello

Solotchin.Eugene

,The reference manual is describing the hardware behavior of the Quad-SPI controller implemented on our STM32 devices.

But, you always have the flexibility to configure the needed pins as GPIO and force them to '0' or '1' depending on the Quad-SPI memory that you are using.Khouloud

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-27 10:20 AM

Ok, thanks.

My PCBs will arrive at the end of this february. I'll try to test QSPI as soon as I assemble them.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-27 11:51 AM

You're welcome .

If you have further questions, do not hesitate to post them on our 'STM32 MCUs Forum'.

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-03-12 10:55 AM

reporting: alternative pinout just works, tested with u-boot sf susbsystem (on full 108 MHz speed, erase, read, write, everything)

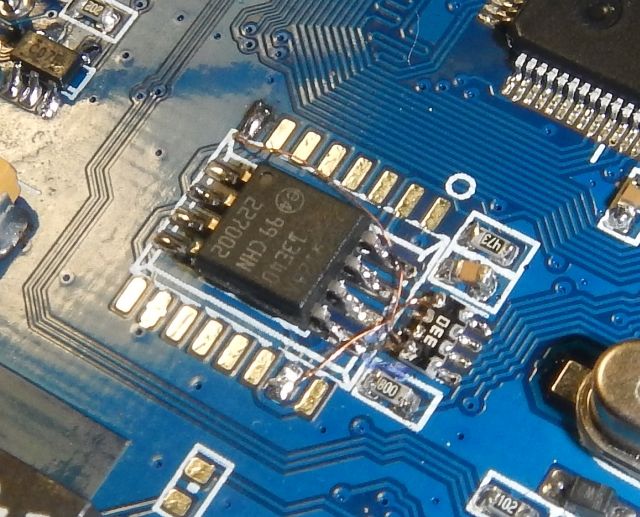

(I've made mistake on this board - accidentally swapped IO0/IO1 pins so it needed some small rework as you can see)

- STM32U535CCT6 Trustzone non-secure is inflashable in STM32 MCUs Security

- STM32WB05: How to change default device name (MP1_XXXXXX) in iBeacon advertising ? in STM32 MCUs Wireless

- Quad-SPI DDR indirect read mode dummy cycles count in STM32 MCUs Products

- STM32F746G-Discovery – HardFault during LwIP Init + Netif setup in STM32 MCUs Embedded software

- Is There Any Working UAC2.0 Example for STM32H7? in STM32 MCUs Embedded software