- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F401RE SPI1 CLK signal wrong

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F401RE SPI1 CLK signal wrong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-25 12:25 PM

I am trying to use the SPI example code, and I configured SPI1 on the NUCLEO-F401RE board in full Duplex work mode.

I connected two NUCLEO-F401RE boards together by GND, CLK, MOSI, MISO,and CS(but I use NSS_Soft mode).

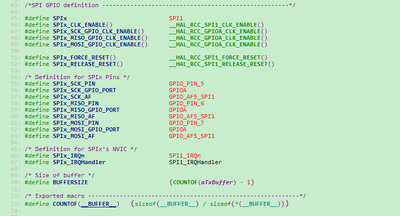

Because there is no example code in the STM32F401RE-Nucleo folder, so I ported the code from STM32F411E-Discovery SPI example code, the original code was configed on the SPI2, but the STM32F401RE-Nucleo only provide the SPI1 on the socket to use. so I changed the SPI2 to SPI1.

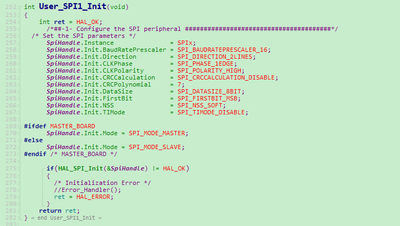

This is my SPI1 Configuration.

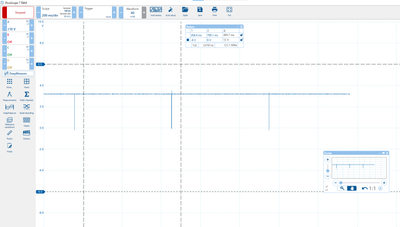

As my uderstand, the clock signal from full duplex SPI master should be continue signal, instead of the clock only enabled during the Master want to sending the message. But when I tried to capture the clock from oscilloscope, I got below image (the clock seems enabled only the master tried to send and receive message).

I set the message to be sent every 500 ms.

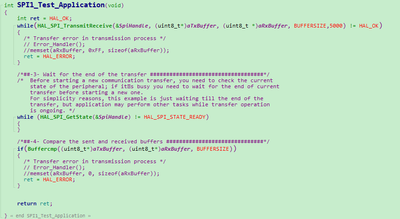

This is my test code (I only use the polling method on the SPI test).

from the test result, If I set the slave and master message sending cycle time are same (for example every 500ms), the master may receive the wrong message, only if the slave cycle time less than master (for example, slave send every 100ms, and master send every 500ms), the message from slave will be right 100%.

But it is a little dramatic, the message read by slave from master side will not wrong whatever the message sending cycle time.

https://github.com/amazingHH/STM32_UART/tree/main/UART_Printf this is the code link.

I will be appreciated, if anyone could help me on this topic!

Kind Regards

RichKnight

Solved! Go to Solution.

- Labels:

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-25 12:39 PM

> As my uderstand, the clock signal from full duplex SPI master should be continue signal, instead of the clock only enabled during the Master want to sending the message.

That is not correct. The SCLK only toggles when the master has data to send (for full duplex SPI).

Since you are using the "polled" version of the SPI calls (HAL_SPI_TransmitReceive()) you don't need a separate check for "transaction complete" - it will by definition be complete when HAL_SPI_TransmitReceive() returns.

The slave cannot send until the master initiates the transfer. The slave should not have a timer on when it tries to send data to the master. It should simply call the transmit/receive function and wait for it to complete. Process the incoming data, prepare the next buffer to send and then call the transmit/receive function.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-25 12:34 PM

> the clock signal from full duplex SPI master should be continue signal

NO.

SPI (master) sending...some clks..end. IF send+receive, you also receive something. Thats it.

If you not "send" , nothing happens.

rtfm.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-25 12:39 PM

> As my uderstand, the clock signal from full duplex SPI master should be continue signal, instead of the clock only enabled during the Master want to sending the message.

That is not correct. The SCLK only toggles when the master has data to send (for full duplex SPI).

Since you are using the "polled" version of the SPI calls (HAL_SPI_TransmitReceive()) you don't need a separate check for "transaction complete" - it will by definition be complete when HAL_SPI_TransmitReceive() returns.

The slave cannot send until the master initiates the transfer. The slave should not have a timer on when it tries to send data to the master. It should simply call the transmit/receive function and wait for it to complete. Process the incoming data, prepare the next buffer to send and then call the transmit/receive function.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-25 3:55 PM

Thank you for your information, It is quite useful, thx again!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-25 3:55 PM

Your reply fixed my problem and thx again!:grinning_face:

- NUCLEO-WB09KE board USUART -> LPUART change fail in STM32 MCUs Wireless

- STM32H7 HRTIM clock drifting? in STM32 MCUs Products

- stm32wb5mm-dk with SAI interface in STM32 MCUs Wireless

- HAL_TIM_IC_ReadChannelCapturedValue returns 0 in STM32 MCUs Embedded software

- CubeMX Route Opamp output to ADC on STM32U3C5CIUxQ in STM32CubeMX (MCUs)