- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F10x interrupt example question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F10x interrupt example question

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-03 8:42 PM

HI.

Currently I'm trying to understand about STM32F10x's interrupt.So I've got some snippet code as the below,

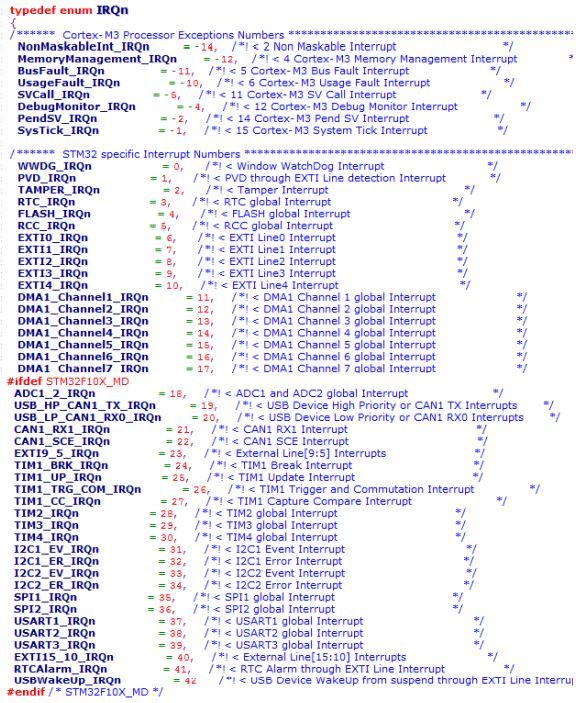

USART1's IRQ number is 37.

// interrupt example snippet code //

unsigned int vector_table_start_addr = *(unsigned int *)0xE000ED08 ; // VTOR register OK.*(unsigned int *)(vector_table_start_addr + (16+37)x4 ) = UART_Handler; // cf) UART_Handler set ??

*(unsigned char *)(0xE000E400+37) = prio;

unsigned int offset = (unsigned int)(37/32)*4; unsigned int bitpos = (unsigned int (37%32); *(unsigned int *)(0xE000E100+offset) &= ~(1<<bitpos);Q1. what does (16+37)x4 mean in *(unsigned int *)(vector_table_start_addr + (16+37)x4 ) = UART_Handler; ??

Would you please let me know how does it come from? and how to understand it?Q2. How does it get

0xE000E400 and 0xE000E100 address number from *(unsigned char *)(0xE000E400+37) = prio; and

*(unsigned int *)(0xE000E100+offset) &= ~(1<<bitpos);

Would you please let me know how does it come from? and how do I understand it?

#stm32f1x-interrupt- Labels:

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-03 9:16 PM

There are 16 slots for 'System Handlers' which are generated via the SCB, the remaining interrupts are generated via the NVIC. The NVIC design maximum is 240 interrupts. ie 240+16 = 256

Each 32-bit register is 4 bytes wide, this is where the *4 comes from. The USART1 interrupt is number 37, and has to index past the 16 system handlers in the vector table, thus the addition.

Look at a listing file when assembling the startup_stm32f10x.s file

The priority registers in the NVIC are 8-bit wide, the USART1 priority is 37 bytes into the priority register array.

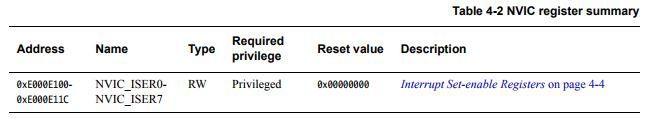

The 37/32 gets you an offset into a 32-bit register file, the *4 gets you from a byte index to a word index, the bitpos 37%32 gets you a bit position within the selected 32-bit register holding the enable bit.

Look at the NVIC documentation in the ARM Technical Reference Manual for the Cortex-M3, understand the bit, byte and word representation of registers with the processors address space.

The example assumes the vector table is in RAM

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-04 2:18 AM

Hi Clive,

I came across the below such as Interrupt Set-enable Register.

and There are 8 Interrupt set-enable registers NVIC_ISER0~7.

But I'm wondering what if I want use interrupt function then should I have to choice the one of 8 registers?

How can we know which NVIC_ISERx should we have to use?

- Stop mode on Threadx with BLE on WBA in STM32 MCUs Wireless

- LSM6DSO I3C SETDASA in STM32 MCUs Embedded software

- I2C STM32CubeMX HAL code: Target receive in interrupt mode TransferDirection issue in STM32 MCUs Embedded software

- STM32H503 – ADC trigger shifting from OFF midpoint at duty > 50% in center-aligned complementary PWM in STM32CubeIDE (MCUs)

- HAL_UARTEx_ReceiveToIdle_DMA gives HAL_ERROR when already receiving in STM32 MCUs Embedded software