Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F103 SPI Slave connection Bug?

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F103 SPI Slave connection Bug?

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 12:59 AM

Posted on July 10, 2017 at 09:59

Hi,

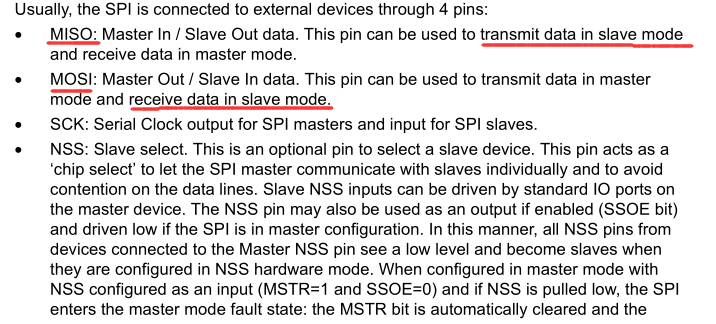

According to the

RM0008.pdf

, when spi in slave mode the MISO pin is transmit data, the MOSI pin is receive data.

But according tests and the example

STM32F10x_StdPeriph_Lib_V3.5.0\Project\STM32F10x_StdPeriph_Examples\SPI\Simplex_Interrupt

,

that is not true.

The truly is MISO is receive data.

Which is error? document? chip?

#spi #stm32f103 #bug

Labels:

- Labels:

-

Bug-report

-

SPI

-

STM32F1 Series

This discussion is locked. Please start a new topic to ask your question.

1 REPLY 1

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-07-10 5:05 AM

Posted on July 10, 2017 at 14:05

MISO = Master mode as Input, Slave mode as Output

MOSI = Master mode as Output, Slave mode as Input

Here no confusion. UART RX/TX is more nasty and usually crossing the lines to make 2 device communicate will happen.

Related Content

- Recommendation on STM board with image processing capacities in Others: STM32 MCUs related

- SPI_WaitOnFlagUntilTimeout() hangs after few cycles of SPI_DMATransmitReceiveCplt() in STM32 MCUs Embedded software

- STM32F401 as I2C Slave Mode? Speed? in STM32 MCUs Products

- I2C MCU Slave register structure conditional ACK/NACK in STM32 MCUs Embedded software

- Time Drift Between 2 Identical Black Pill boards in STM32 MCUs Products