- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- MPU Setup on STM32F4 MCU failed

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPU Setup on STM32F4 MCU failed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-10-05 2:34 AM

Dear Forum,

I am setting up the MPU of a STM32F401CE using a bare metal system. All tasks and handlers run inPriviledge Mode, therefore I want to enable certain areas for priviledged access, background should cause a memfault. I use the following memory map and MPU setup:

/********************************************//**

* \name HAL_MCU_MPUSetup

* \brief Setup der MPU

* \details

No. Memory Address Type Access Permissions Size Comment

0 Flash 0x08020000 Normal Full access, RO 128KB Priviledged Read Only

1 SRAM1 0x20000000 Normal Full access, RW 64KB

2 SRAM2 0x20010000 Device Full access, RW 16KB

4 DMABUF 0x20014000 Device Full access, RW 16KB Strongly Ordered, da DMA Multimaster

5 PPB 0xE0000000 Device Full access, RW 1MB

***********************************************/

void HAL_MCU_MPUSetup(void)

{

/* Disable MPU */

ARM_MPU_Disable();

// Application Flash Area

MPU->RBAR = ARM_MPU_RBAR(0, 0x08020000);

MPU->RASR = ARM_MPU_RASR(0, ARM_MPU_AP_FULL, 0, 0, 1, 0, 0, ARM_MPU_REGION_SIZE_128KB);

// SRAM1 Kachel

MPU->RBAR = ARM_MPU_RBAR(1, 0x20000000);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_FULL, 0, 1, 0, 1, 0, ARM_MPU_REGION_SIZE_64KB);

// SRAM2 Kachel

MPU->RBAR = ARM_MPU_RBAR(2, 0x20010000);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_FULL, 0, 1, 0, 1, 0, ARM_MPU_REGION_SIZE_16KB);

// DMABUF Buffer is Multimaster Shareable (Strongly Ordered!)

MPU->RBAR = ARM_MPU_RBAR(3, 0x20014000);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_FULL, 0, 1, 0, 1, 0, ARM_MPU_REGION_SIZE_16KB);

/* 1MB PPB (Privileged, XN, Read-Write) */

//MPU->RNR = 5;

MPU->RBAR = ARM_MPU_RBAR(4, 0xE0000000);

MPU->RASR = ARM_MPU_RASR(1, ARM_MPU_AP_FULL, 0, 0, 0, 0, 0, ARM_MPU_REGION_SIZE_1MB);

/* Enable MPU */

ARM_MPU_Enable(0u);

}

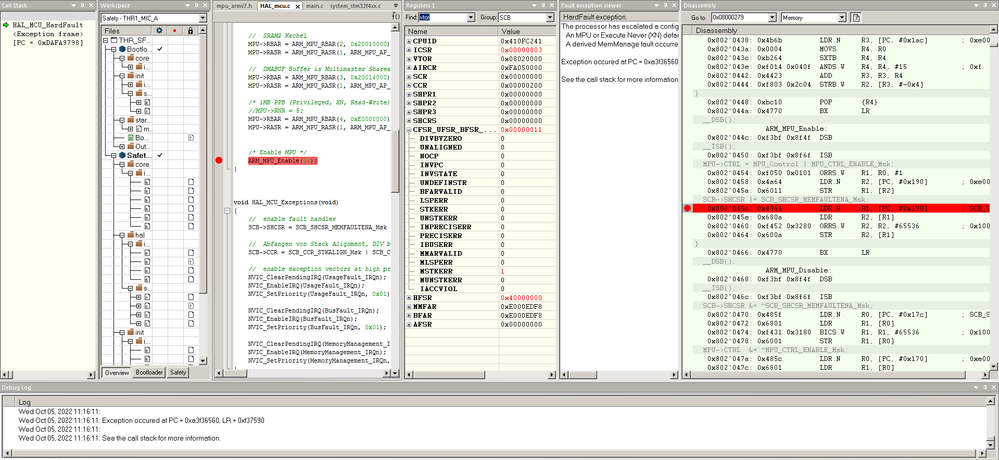

When enabling the MPU I get a a hard fault exception when accessing the SCB->SHCSR Register (@ addr. 0XE000EDF8. See marked line in Dissasembly Windows. The Fault Viewer dumps following message:

The processor has escalated a configurable-priority exception to HardFault.

An MPU or Execute Never (XN) default memory map access violation has occurred on an instruction fetch (CFSR.IACCVIOL, MMFAR).

A derived MemManage fault occurred on exception entry (CFSR.MSTKERR, MMFAR).

Exception occured at PC = 0xa3f36560, LR = 0xf37590

See the call stack for more information.following question:

Q1. How do I give correct access priviledge for Cortex Internal peripferals? (starting @0xE0000000

Q2. I use certain Area of the internal SRAM as DMA Buffer, how which memory attributes are correct for Multimaster access (TEX, C,S,H Bits) and can I even give different attributes for parts of the memory (DMABUF Area) this is located on the same device?

regards,

Lorenz

- Labels:

-

DMA

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-10-05 2:36 AM

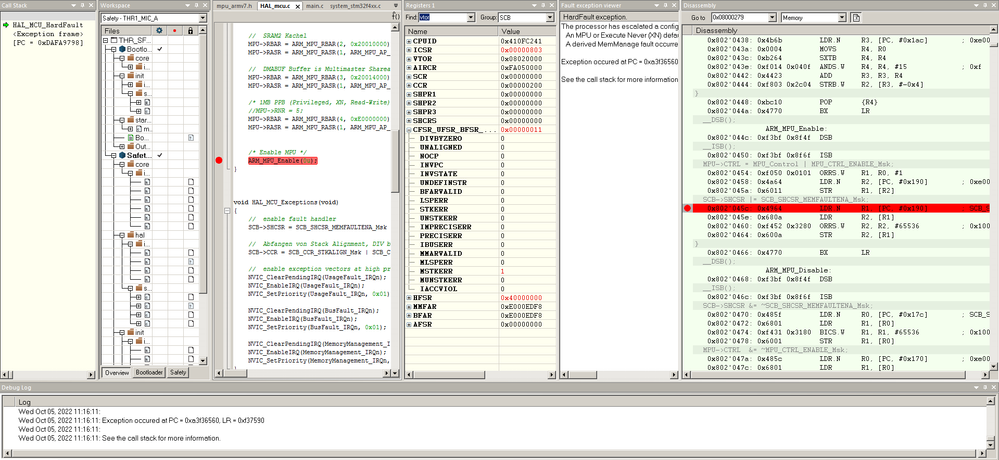

Following Image of debugger I got:

- Cannot find/enable CMSIS-DSP (arm_math.h) on STM32N6570-DK via STM32CubeMX in STM32CubeMX (MCUs)

- STM32CUBE RTOS view not working when debugging running target with just symbolFileName supplied to imagesAndSymbols in STM32CubeIDE for Visual Studio Code (MCUs)

- Wild issue! STM32H7S78 stuck after DA provisioning! in STM32 MCUs Security

- STM32F4 data length assert failed for HAL_SPI_TransmitReceive_DMA in STM32 MCUs Embedded software

- STM32F103RB Nucleo – Debug fails after programming (“Target is not responding” in ST-LINK GDB Server) in STM32 MCUs Boards and hardware tools