- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Dual bank execution from Bank2 (STM32L071)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Dual bank execution from Bank2 (STM32L071)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-17 1:42 PM

Hi,

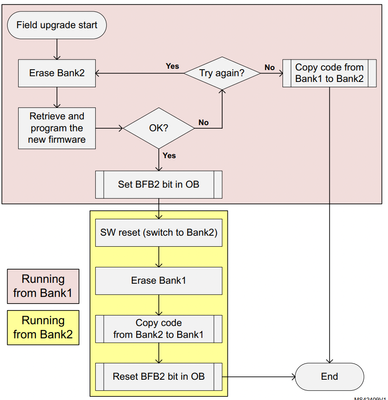

According to some of the on-the-fly firmware update documents, update is done with the following steps:

- program the new firmware to Bank2

- set BFB2 bit to start executing from Bank2

- while in Bank2, copy the code from active Bank2 to Bank1

- reset BFB2 to continue executing code from Bank1

Doing some small tests, I realized that it was fine to continue running new firmware in Bank2 until next firmware update is needed, without double programming and jumping Bank1 -> Bank2 -> Bank1.

My question: Is there any disadvantage to continue executing new firmware from Bank2 until the newer firmware is available (and then programmed to Bank1)? Or is it really necessary to always run the main firmware from Bank1 (and use Bank2 just during the update)?

Note: I run tests with a simple program. Maybe I am missing some functionality which will not work on more complex programs on the long run executed from Bank2. Or my assumptions are just wrong.

Thanks,

Zoran

Solved! Go to Solution.

- Labels:

-

Flash

-

STM32L0 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-03 1:31 AM

After two weeks of further testing, I just wanted to provide additional feedback on this topic. We are running our main firmware alternatively on both banks, and there are no performance-wise differences or any additional code to verify which bank is being used. The FOTA update is the same, as it is always the 'other' bank being deleted and flashed.

However, the only deviation from a regular work flow is EEPROM. As it is also two-bank-based access, we are simply copying the EEPROM content from one bank to another during the OTA update.

One extremely important step is to always assign a vector table to 0x8000000 at the very beginning of the main code.

SCB->VTOR = 0x08000000;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-17 2:45 PM

From a performance standpoint, there are no issues with running in bank 2 indefinitely. The two banks should have identical behavior. And as you saw, you can boot from bank 2 by setting the appropriate option bits.

From a program logic standpoint, it might be useful to always run in bank 1 to make the update process the same each time, as opposed to having to figure out which bank you're in and program bits accordingly and make sure you erase the correct bank.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-18 2:21 AM

Hello @zoranr

The two banks have similar behavior. The number of wait states depends on the voltage scaling range. Performance is almost linear in relation to the frequency. According to data retention, it depends on the number of program/erase cycles and temperature, not a specific bank.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Best regards,

FBL

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-03 1:31 AM

After two weeks of further testing, I just wanted to provide additional feedback on this topic. We are running our main firmware alternatively on both banks, and there are no performance-wise differences or any additional code to verify which bank is being used. The FOTA update is the same, as it is always the 'other' bank being deleted and flashed.

However, the only deviation from a regular work flow is EEPROM. As it is also two-bank-based access, we are simply copying the EEPROM content from one bank to another during the OTA update.

One extremely important step is to always assign a vector table to 0x8000000 at the very beginning of the main code.

SCB->VTOR = 0x08000000;

- STM32H753 QUADSPI – Clarification on Dual Bank, IO Lines, and Multi-Flash Possibilities in STM32 MCUs Products

- STM32L496 firmware >512 KB - dual-bank flash overlap (normal execution + OTA) in STM32 MCUs Products

- can't erase correct Flash Bank when attempting to switch from Bank2 to Bank1 in STM32 MCUs Products

- Stm32l072KZ Firmware Update in STM32 MCUs Products