- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- [STM32F767] Shift occurs when reading NAND memory ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[STM32F767] Shift occurs when reading NAND memory data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-05 10:56 PM

Dear all

nand memory device is MT29F4G. I attacing datasheet

first nand memory setting.

===========================================================

hnand1.Instance = FMC_NAND_DEVICE;

/* hnand1.Init */

hnand1.Init.NandBank = FMC_NAND_BANK3;

hnand1.Init.Waitfeature = FMC_NAND_WAIT_FEATURE_ENABLE;

hnand1.Init.MemoryDataWidth = FMC_NAND_MEM_BUS_WIDTH_8;

hnand1.Init.EccComputation = FMC_NAND_ECC_ENABLE;

hnand1.Init.ECCPageSize = FMC_NAND_ECC_PAGE_SIZE_2048BYTE;

hnand1.Init.TCLRSetupTime = 0;

hnand1.Init.TARSetupTime = 0;

/* hnand1.Config */

hnand1.Config.PageSize = 2048;

hnand1.Config.SpareAreaSize = 64;

hnand1.Config.BlockSize = 64;

hnand1.Config.BlockNbr = 2048;

hnand1.Config.PlaneNbr = 2;

hnand1.Config.PlaneSize = 2048;

hnand1.Config.ExtraCommandEnable = DISABLE;

/* ComSpaceTiming */

ComSpaceTiming.SetupTime = 5;

ComSpaceTiming.WaitSetupTime = 5;

ComSpaceTiming.HoldSetupTime = 6;

ComSpaceTiming.HiZSetupTime = 0;

/* AttSpaceTiming */

AttSpaceTiming.SetupTime = 5;

AttSpaceTiming.WaitSetupTime = 5;

AttSpaceTiming.HoldSetupTime = 6;

AttSpaceTiming.HiZSetupTime = 0;

============================================================

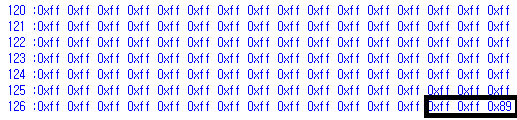

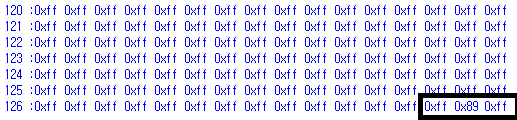

when I read NAND nomal:

When I read Nand , data is shift

HAL_NAND_Read_Page_8b source :

=====================================================================

{

*(__IO uint8_t *)((uint32_t)(deviceAddress | ADDR_AREA)) = 0x00;

__DSB();

*(__IO uint8_t *)((uint32_t)(deviceAddress | ADDR_AREA)) = 0x00;

__DSB();

*(__IO uint8_t *)((uint32_t)(deviceAddress | ADDR_AREA)) = Third_Address;//ADDR_1ST_CYCLE(nandAddress);

__DSB();

*(__IO uint8_t *)((uint32_t)(deviceAddress | ADDR_AREA)) = Fourth_Address;//ADDR_2ND_CYCLE(nandAddress);

__DSB();

*(__IO uint8_t *)((uint32_t)(deviceAddress | ADDR_AREA)) = Fifth_Address;//ADDR_3RD_CYCLE(nandAddress);

__DSB();

}

}

*(__IO uint8_t *)((uint32_t)(deviceAddress | CMD_AREA)) = NAND_CMD_AREA_TRUE1;

__DSB();

for(; index < size; index++)

{

*(uint8_t *)pBuffer++ = *(uint8_t *)deviceAddress;

}

=========================================================================

when I test on ST32F407 , it is working well.

But when I test on ST32F767 , data is shift.

Let me know why this is happening.

Thanks.

- Labels:

-

STM32Cube MCU packages

-

STM32F7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-06 12:21 AM

I don't attempt to understand the problem, but try to set the FMC area where the NAND is located as Device in MPU.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-06 5:22 AM

The NAND reads like a FIFO, so will be sensitive to access cycles.

Don't view the memory in a debugger window.

Configure the MPU to not cached or buffer the memory area.

Suggest also moving efficiently as words rather than bytes.

For support work with your local ST FAE

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-06 7:39 AM

Clive,

> Configure the MPU to not cached

I think it's not enough and it ought to be set as Device, to prevent read restarts (Device precludes automatically caching).

> buffer the memory area.

Can you please elaborate?

Thanks,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-06 7:58 AM

Relates to completion, you shouldn't need the fencing instructions if the memory space is described correctly, and it stops the writes being deferred.

To quote an ARM engineer

"bufferable write to a peripheral register is faster than non-bufferable write (if non-bufferable, the processor needs to wait for the write to complete before next instruction can execute)."

Trying to avoid Write Buffers, and Write-Back or Write-Thru behaviours.

I'd probably use a volatile cast in the memory copy used by the OP

The use of LDM might also have undesirable restart behaviour on FIFO memory.

Up vote any posts that you find helpful, it shows what's working..

- Using VREFINT on STM32C071K8U6 for battery measurement with variable VDDA in STM32 MCUs Products

- GPDMA in Linked List with OCTOSPI in STM32 MCUs Embedded software

- Arbitrary waveform by timer using DMA in STM32 MCUs Embedded software

- STM32U535 LPBAM LPTIM3 capture problem in STM32 MCUs Embedded software

- External QSPI NOR flash read and write operation in STM32 MCUs Embedded software