- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- SPI suitable for this?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI suitable for this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-28 9:11 PM

Hey everyone,

I have a quick question,

I have the following chip:

http://www.analog.com/media/en/technical-documentation/data-sheets/AD7761.pdf

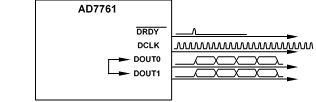

It provides the following output when daisy chained(as I'll be using it this way)

So two data lines, one data ready and a data clock running at 24 MHz with rise and fall times of 1 ns.

I'm thinking of using two SPI lines coupled to the data lines, coupling the DCLK to both and then generating a chip select using timers, As soon as the drdy goes low, data starts coming out up until all the bits of the sample are out, then the lines go low until the next drdy. I'd like to generate a chip select using timers that envelopes the data from the drdy falling edge up to the point where all the bits are out(prior to the lines going low).

I plan on using a dma (double buffer mode) on each spi line so that I can send the data out to a SD card via 4 bit SDIO while the spi lines fill the second buffer.

Will this be something I can accomplish with an STM32f722ze using HAL?

Thank in advance for any help

#general-purpose-timers #hal-spi #dma-sdmmc- Labels:

-

SDIO-SDMMC

-

STM32Cube MCU packages

-

TIM

- STM32H7B3LIH6Q – TFT RGB selection and HDMI support in Others: STM32 MCUs related

- Error installing C5xx HAL drivers pack: "Unable to get local issuer certificate" in STM32CubeMX2 (MCUs)

- NUCLEO-F446RE: Dual SiPM Signal Acquisition and Coincidence Detection in Others: STM32 MCUs related

- WiFi or WiFi+BT modules architecture and parts recommendations in STM32 MCUs Wireless

- Recommend a BLE SoC with Eddystone support ? in STM32 MCUs Wireless