- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Problem with TX CLK for MII interface (analog swit...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Problem with TX CLK for MII interface (analog switch between PC3_C and PC3)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 3:02 AM

Hi.

I have a problem with MII PHY interface STE100P connected to STM32H743ZIT6 (package LQFP144). Communication works only on 10Mbps. On 100Mbps works only packet receiving. Transmitting is not working at all. I spend several weeks to find why. And now I finally know why.

When the PHY is connected to 100Mbps network, TX state machine stops processing TX descriptors (OWN bit stuck on 1 - DMA owns the descriptor). Also "Flush Transmit Queue" never ends.

Problem is with the TX_CLK signal connected to PC3_C pin on LQFP144 package variant. With 10Mbps speed the clock signal is 2.5MHz. With 100Mbps the clock signal is 25Mhz.

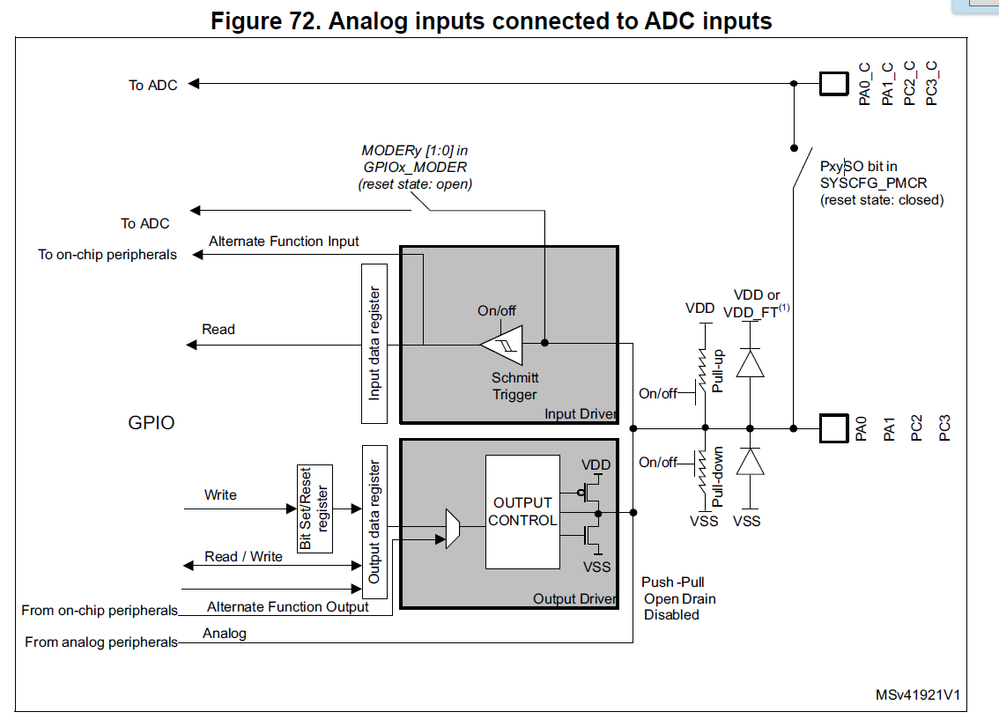

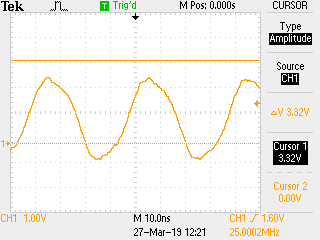

ETH_MII_TX_CLK signal is connected to PC3 and through the analog switch, it is connected to PC3_C. The analog switch can be closed by setting 0 to PC3SO in SYSCFG_PMCR register. The problem is in this analog switch itself because it doesn't have enough throughput for 25MHz signal clock and TX state machine lost the clock and stops working. It works only witch signal amplitude increased to 4V on PC3_C pin. With 3.3V it doesn't work because of high attenuation of an analog switch with 25Mhz signal.

RX clock is working because it can be connected directly to PA1 without an analog switch. PC3 pad is available only on TFBGA240+25 package.

This should be somehow fixed or noticed in the documentation or errata sheet.

Analog switch

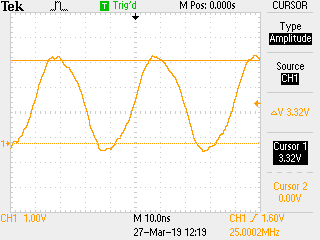

Working with increased voltage to 4V peek-peek

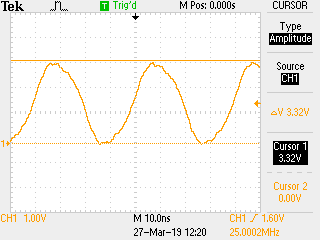

Not working with 3V peek-peek

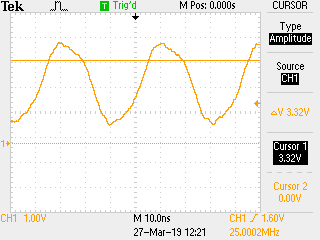

Not working with voltage +shift

Not working with voltage -shift

- Labels:

-

Bug-report

-

Ethernet

-

STM32H7 series

- Ask for I3C support on NUCLEO-H563ZI (MB1404C) in STM32 MCUs Embedded software

- SPI3 hangs after some time in STM32 MCUs Embedded software

- Cannot find/enable CMSIS-DSP (arm_math.h) on STM32N6570-DK via STM32CubeMX in STM32CubeMX (MCUs)

- STM32N6570-DK – Ethernet TX Failure & Camera Frame Not Received in STM32 MCUs Embedded software

- UART does not work with STM32U575 in STM32 MCUs Boards and hardware tools