- STMicroelectronics Community

- Automotive and Transportation

- Automotive MCUs

- SPC570s-DISP board: FlexCAN sends bad frames indep...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPC570s-DISP board: FlexCAN sends bad frames independent of CAN parameters

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-18 05:33 AM

Hello,

I have similar problem with the SP570S-DISP board as described here:

My Configuration: 250KBaud, 16Tq, Sample-point=75%, XOSC 40MHz, CAN_clk 40 MHz, V_ext=12V/VDD_HV_IO=5V, Vector VN1610+CANoe running, 120 Ohm on both sides, ID=0x135, Data={0xAA, 0x55, 0x00, 0x00, 0xAA, 0x55, 0x00, 0x00} DLC=8.

Clock settings:

/* Setting the system dividers to their final values.*/

/*

* b0 : DE = 0b1 enable divider

* b9-15 : DIV (Divider is DIV + 1)

*/

/* System clock 0 divider */

MC_CGM.SC_DC0.R = 0x80000000UL;

/* System clock 1 divider */

MC_CGM.SC_DC1.R = 0x80010000UL;

/* System clock 2 disabled */

MC_CGM.SC_DC2.R = 0UL;

/* Pit clock divider 5 */

MC_CGM.AC0_DC0.R = 0x80040000UL;

/* SAR ADC clock divider 25 */

MC_CGM.AC0_DC1.R = 0x80180000UL;

/* CTU clock divider 25 */

MC_CGM.AC0_DC2.R = 0x80180000UL;

/* DSPI clock divider 4 */

MC_CGM.AC0_DC3.R = 0x80030000UL;

/* LinFlex clock disabled */

MC_CGM.AC0_DC4.R = 0UL;

/* eTimer clock divider 4*/

MC_CGM.AC0_DC5.R = 0x80030000UL;

/* FlexCAN clock divider 1 */

MC_CGM.AC1_DC0.R = 0x80000000UL;

/* Setting the clock selectors for PIT, SAR, CTU, DSPI, LinFlex, eTimer: PLL_0 */

/*

* b4-7: SELCTL (Auxiliary clock source selection control)

* */

MC_CGM.AC0_SC.R = 0x02000000UL;

/* Setting the clock selectors for FlexCAN: XOSC (external oscillator) */

MC_CGM.AC1_SC.R = 0x01000000UL;

/* Setting the clock selectors for PLL_0: XOSC (external oscillator) */

MC_CGM.AC2_SC.R = 0x01000000UL;

/* Setting the clock selectors for PLL_1: XOSC (external oscillator) */

MC_CGM.AC3_SC.R = 0x01000000UL;FlexCAN settings:

uint8_t mb_index = 0;

/* set peripheral clock mode.*/

cpu_set_peripheral_clock_mode(79U, 0x12);

/* external clock source */

FLEXCAN_0.CTRL.B.CLK_SRC = 1U;

/* Empty all mailboxes */

for (mb_index = 0; mb_index < 8U; mb_index++) {

FLEXCAN_0.MB[mb_index].MB_CS.R = 0UL;

FLEXCAN_0.MB[mb_index].MB_ID.R = 0UL;

FLEXCAN_0.MB[mb_index].MB_DATAL.R = 0UL;

FLEXCAN_0.MB[mb_index].MB_DATAH.R = 0UL;

}

/* Enable the device.*/

FLEXCAN_0.MCR.B.MDIS = 0U;

while (0 == FLEXCAN_0.MCR.B.LPM_ACK)

;/* wait until module is enabled */

FLEXCAN_0.MCR.B.FRZ = 0b1;

FLEXCAN_0.MCR.B.HALT = 0b1;

while (0 == FLEXCAN_0.MCR.B.FRZ_ACK)

;/* enter freeze mode */

FLEXCAN_0.MCR.B.MAXMB = 7U;

FLEXCAN_0.MCR.B.SUPV = 0b0; /* deactivate super-visor mode */

FLEXCAN_0.MCR.B.SRX_DIS = 0b1; /* No self reception*/

FLEXCAN_0.MCR.B.FEN = 0b0; /* No Fifo */

FLEXCAN_0.MCR.B.AEN = 0b0; /* No Abort enable */

FLEXCAN_0.MCR.B.WRN_EN = 0b1;

FLEXCAN_0.MCR.B.LPRIO_EN = 0b0; /* no prio */

(void) FLEXCAN_0.TIMER.R; /* Unlock message buffer */

/* RX MB initialization.*/

for (mb_index = 0U; mb_index < 4U; mb_index++) {

FLEXCAN_0.MB[mb_index].MB_CS.B.CODE = 4U;

}

/* TX MB initialization.*/

for (mb_index = 4U; mb_index < 8U; mb_index++) {

FLEXCAN_0.MB[mb_index].MB_CS.B.CODE = 8U;

}

FLEXCAN_0.CTRL.B.PSEG1 = 5U;

FLEXCAN_0.CTRL.B.PSEG2 = 3U;

FLEXCAN_0.CTRL.B.PROPSEG = 4U;

FLEXCAN_0.CTRL.B.PRESDIV = 9U;

FLEXCAN_0.CTRL.B.RJW = 1U;

FLEXCAN_0.CTRL.B.SMP = 0b0;

FLEXCAN_0.CTRL.B.LBUF = 0b1; /* Lowest buffer first */

FLEXCAN_0.CTRL.B.TWRN_MSK = 0b1;

FLEXCAN_0.CTRL.B.RWRN_MSK = 0b1;

FLEXCAN_0.CTRL.B.BOFF_MSK = 0b1;

FLEXCAN_0.CTRL.B.ERR_MSK = 0b1;

FLEXCAN_0.CTRL.B.LOM = 0b0; /* listen-only */

FLEXCAN_0.CTRL.B.LPB = 0b0; /* loop back */

FLEXCAN_0.CTRL.B.TSYN = 0b0;

FLEXCAN_0.MCR.B.FRZ = 0U;

while (1 == FLEXCAN_0.MCR.B.FRZ_ACK)

;/* leave freeze mode */

/* IRQ setting for TX buffers */

FLEXCAN_0.IMASK1.R = 0xFFFF0000UL;

/* Clear interrupt flags with ones */

FLEXCAN_0.IFLAG1.R = 0xFFFFFFFUL;

/* Synchronize to CAN bus */

FLEXCAN_0.MCR.B.HALT = 0U;Transmit section:

/* clear IRQ flags with ones */

FLEXCAN_0.IFLAG1.R = 0xFFFFFFFUL;

/* Lock message buffer */

(void) FLEXCAN_0.MB[0].MB_CS.B.CODE;

/* clear data fields */

FLEXCAN_0.MB[buffer].MB_DATAL.R = 0U;

FLEXCAN_0.MB[buffer].MB_DATAH.R = 0U;

/* inactivate buffer */

FLEXCAN_0.MB[buffer].MB_CS.B.CODE = 0b1000;

FLEXCAN_0.MB[buffer].MB_ID.R = frame->id << 18U;

/* Fill in data...*/

FLEXCAN_0.MB[buffer].MB_CS.B.LENGTH = frame->dlc;

FLEXCAN_0.MB[buffer].MB_CS.B.IDE = 0U; /* standard id */

FLEXCAN_0.MB[buffer].MB_CS.B.RTR = 0U; /* data frame */

FLEXCAN_0.MB[buffer].MB_CS.B.SRR = 0U;

/* start transmission */

FLEXCAN_0.MB[buffer].MB_CS.B.CODE = 0b1100;EDIT:

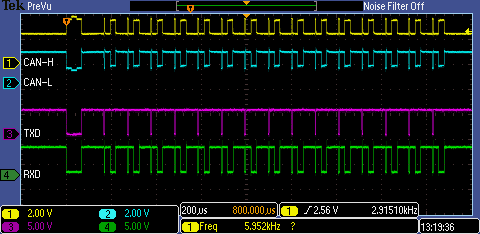

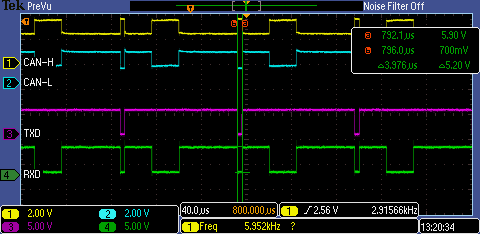

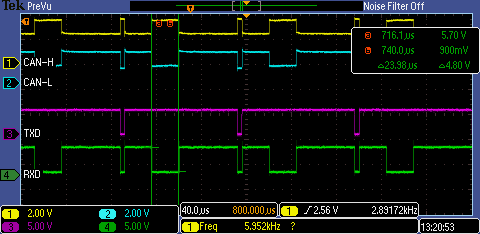

I am getting directly after transmit with "buffer" set to a TXD buffer this signal on the bus:

(obviously CANoe is sending error frames)

I discovered when I do a non fitting initialization of message boxes but with a number less than the MAXMB value then I get this signal instantly after FLEXCAN_0.MCR.B.FRZ = 0U during init.

And I have the same problem with the examples delivered with SPCStudio.

With Loop-back activated there are no problems.

Thank you in advance!

Regards

Ben

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-03-21 04:45 AM

Hi,

I think that there is a problem in pads configuration.

Please configure the right RX and TX pads as showed in the below example:

/* Setup FlexCAN 0 pins */

/* TX (PB0)

PA = 1 (AF1) / OBE = 1 / ODE = 1 / WPE = WPS = SRC (min value) = 0 */

SIU.PCR[16].R = 0x0620;

/* RX (PB1) IBE = 1 */

SIU.PCR[17].B.IBE = 0x1;

Best regards

Domenico