- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- IIS3DWB over I2C. I know SPI is preferred but I h...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IIS3DWB over I2C. I know SPI is preferred but I have severe space restrictions and the extra 3 signals for SPI is a problem. So questions refer to I2C comms.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-24 11:19 AM

- Are there any I2C communication timings available available. Trials seem to indicate device is performing clock stretching and only achieving 200kHz on returned data.

- FIFO usage. To reduce impact of I2C overhead, I would like use single axis mode on Z axis. If I use the 1AX_TO3REGOUT feature (CNTL4), can I restrict FIFO content to Tag and three Z axis readings. This alone would reduce I2C overhead. (ie 3 data sample per I2C read sequence using auto register increment)

- Is there a method to burst read out of the FIFO, via I2C or do we need to always use a 7 byte read preceded with a register setup address of 0x78.

Comments very welcome

- Labels:

-

Accelerometers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-25 8:18 AM

Hi @GBroo.2 ,

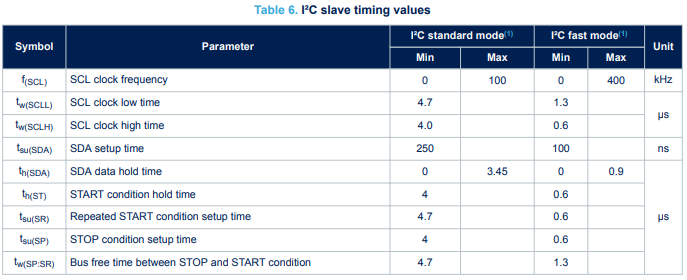

>> Are there any I2C communication timings available available.

The digital block of the I2C for the IIS3DWB is similar to other ST devices, especially the IIS2ICLX.

>> Can I restrict FIFO content to Tag and three Z axis readings

>> Is there a method to burst read out of the FIFO?

I'm afraid that the FIFO usage is the one that you depicted, i.e. you have to deal with the 7 bytes and the FIFO_DATA_OUT 3-axis pattern. I'm however not able to try your configuration right now, but if you can try them it can be useful.

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-07-21 8:28 AM

@GBroo.2 Hi Dear,

Can you help me with I2C code? Basic configuration? I am unable to read data. Thanks