- STMicroelectronics Community

- Knowledge base

- STM32 MCUs

- How to set up the LTDC peripheral to interface wit...

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

How to set up the LTDC peripheral to interface with the display panel ATM0500D27-CT from AZ Displays

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

on

2021-12-03

8:35 AM

- edited on

2025-11-25

2:46 AM

by

![]() Laurids_PETERSE

Laurids_PETERSE

1. Introduction

The STM32’s integrated LTDC (LCD-TFT Display Controller) peripheral can be used to interface with parallel displays. It is very common for HMI-of-Things applications to have the capability to control and display data between user and machine.

In this article we will see how to configure the LTDC peripheral of the STM32 to interface with ATM0500D27-CT from AZ Displays – datasheet available in the link below:

https://www.azdisplays.com/PDF/ATM0500D27-CT.pdf

The display panel is available for mass market from Digi-Key:

https://www.digikey.com/en/products/detail/az-displays/ATM0500D27-CT/13236094

2. Prerequisites

- Microcontroller: STM32F750N8

- Software: TouchGFX Designer and STM32CubeMx

In this article we’ll see what changes need to be made to the LTDC configuration in the STM32F7508-DK TouchGFX Board Setup (TBS) to support the display panel ATM0500D27-CT.

3. Steps

-

Create TouchGFX application

-

Open the STM32CubeMx project

|

|

-

Set up the LTDC clock

When we look at the display panel datasheet, we see the specification of the pixel clock or dot clock “DCLK”. This pixel clock is the speed at which pixels are transmitted. It is specified in MHz and for this panel it is 25MHz typ.

|

In STM32CubeMx, under the Clock Configuration Tab, is where the pixel clock is set up. As shown below, the LCD-TFT clock is derived from PLLSAI1. Thus, we need to set up the PLLSAI1 “N” multiplier, “R” and the divider right after the output of the PLLSAI1 in a way to get 25MHz to the LCD-TFT.

One possible solution is to have N = 100, R = 2, and the divider right after the output of the PLLSAI1 = 2 . This solution gives a pixel clock of 25MHz.

-

Set up the display type

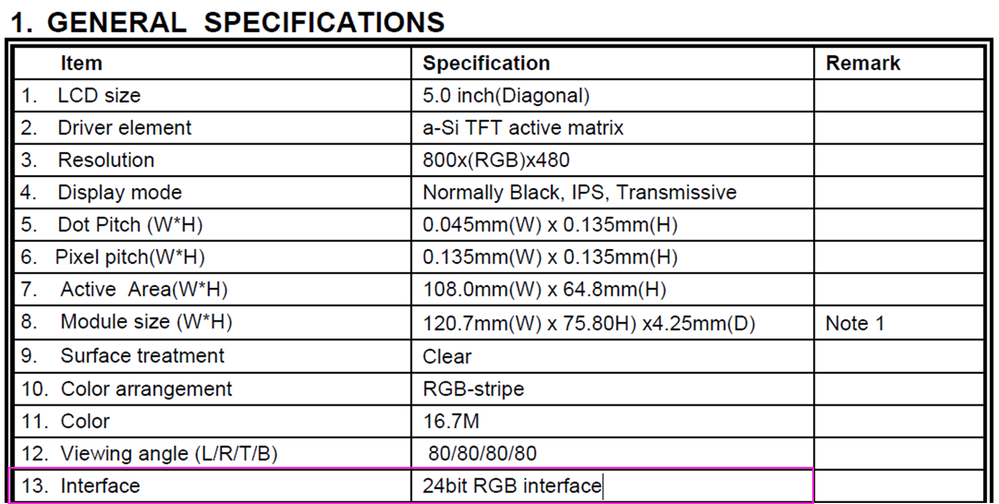

When we look at the general specifications of the display panel, we see the display interface supports 24-bit RGB:

Under Pinout & Configuration Tab, we select Multimedia category and then LTDC peripheral. Under LTDC Mode and Configuration, we select the display Type: RGB888 (24 bits).

|

-

Setup the horizontal and vertical timings

- The horizontal timings highlighted below gives a display period of 800 which is the same as display width. Besides, it gives a back porch of 8, a front porch 8, and a pulse width or horizontal synchronization width of 4.

|

|

- The same timing table in the datasheet of the display gives the vertical timings: display period of 480 which is the same Active height. Besides, it gives a back porch of 8, a front porch 8, and a pulse width or vertical synchronization width of 4.

|

|

-

Signal Polarity

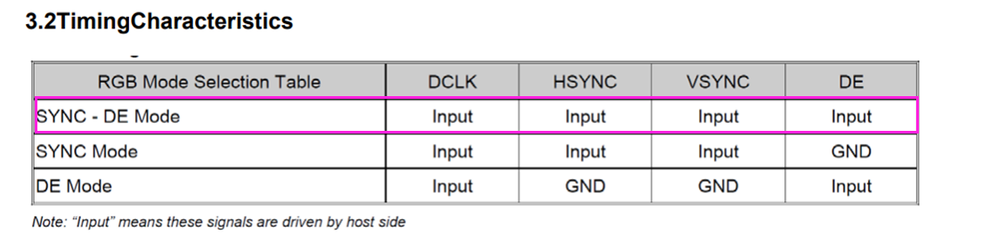

The display panel supports three modes: SYNC mode, SYNC-DE mode, and DE mode. We’re more interested in SYNC-DE mode as it uses the three signals: Pixel clock (DCLK), HSYNC, VSYNC, and Data Enable (DE).

The display panel has already VDPOL and HDPOL tied to High. This means the VSYNC and HSYNC are active low. Besides, the figure below shows the DE signal is active high.

|

Based on the signal polarity given by the datasheet of the display panel, we provision the configuration under Signal Polarity.

|

-

Set up the layer settings

- Horizontal Stop to the display width which is 800

- Vertical stop to the display height which is 480

- Pixel format to the display type which is RGB888

- Frame buffer Line Length to the display width which is 800

- Frame buffer number of lines to the display width which is 480

|

4. Links

STM32F7508N8 – Datasheet

STM32F75xxx and STM32F74xxx advanced arm based 32-bit MCUs- Reference manual

STM32CubeMx - STM32Cube initialization code generator

STM32F7508-DK - Discovery kit with STM32F750N8 MCU

AN4861: LCD-TFT display controller (LTDC) on STM32 MCUs - Application Note

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Email to a Friend

- Report Inappropriate Content

Hi Laura,

I was using your guide to setup an AZ display. However, I am not able to change the color within the hltdc.Init.Backcolor to ensure proper functionality, it remains all white. I want to make sure I do not have something configured wrong and determine if it's hardware related. Can you please let me know if a setting seems off to you?

I’m using a custom board with a STM32F479BIT6 (PH0/PH1 8Mhz oscillator only) interfacing with a ATM0500D27K.

RCC config:

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Email to a Friend

- Report Inappropriate Content

Hi @Laura C. , thanks a lot for your post. Just a small note:

"Only the DE control signal must be inverted versus the DE polarity indicated in the display

datasheet. The other control signals must be configured exactly like the display datasheet."

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Email to a Friend

- Report Inappropriate Content

Hi,

I have setup the STM32F7508-DK according to the article published by ST, I am using 7" 800x480 TFT with the STM32F7508-DK Board, The Problem lies when the Image is updated for there is the transition of Screens, I.e The Screen Updates randomly in a blocked fashion, I am unable to find the issue, I would appreciate if you could provide some lead on the same.