- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs TouchGFX and GUI

- DCMI-VSYNC and FSMC-NADV pin no 93 colision probl...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DCMI-VSYNC and FSMC-NADV pin no 93 colision problem in STM32F207.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-25 5:27 AM

Hi,

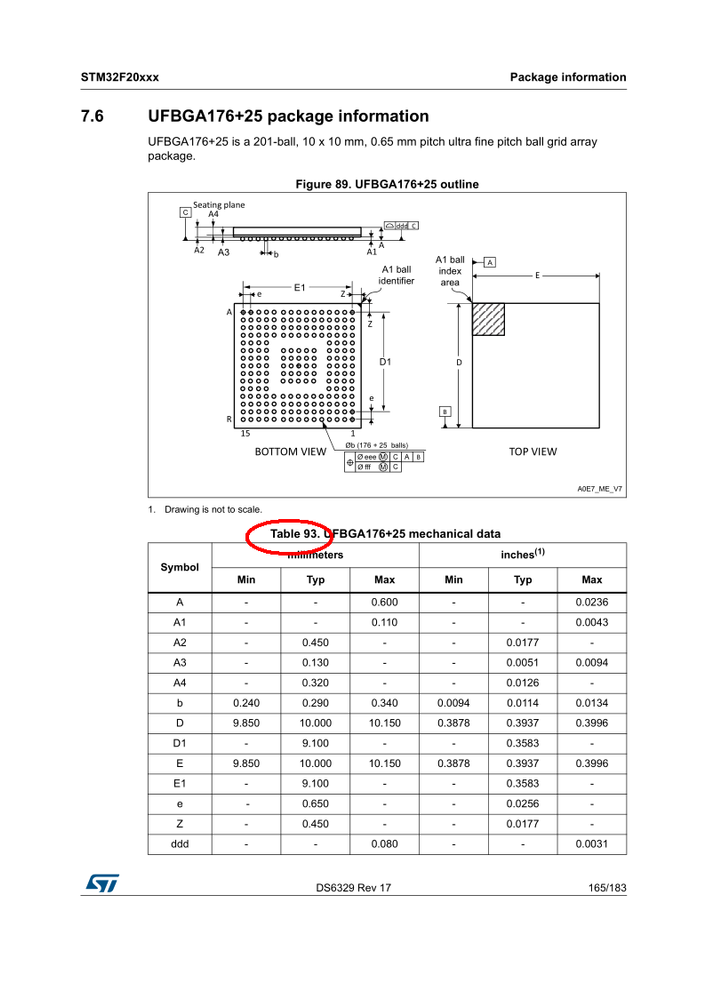

I am designing device using 100 pin STM32F207 mcu and I was planning to connect camera to DCMI peripheral and SRAM to multiplexed FSMC using latches. But in process of drawing schematic I noticed that FSMC pin that controls latches (FSMC_NL or FSMC_NADV) is also DCMI_VSYNC and there is no alternative pin for that. Although in table 93 in datasheet it is shown that it is possible to use DCMI and muxed SRAM together.

Is there any solution for this problem or I need to go for 144 pin controller?

Thank you!

- Labels:

-

DCMI

-

FMC-FSMC

-

STM32F2 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-25 11:22 AM

Looking into DS, it appears you'll need to go for the 176-pin one.

> Although in table 93 in datasheet it is shown that it is possible to use DCMI and muxed SRAM together.

?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-26 4:49 AM

Thank You for your answer.

UPBGA package have two pins with DCMI-VSYNC function. On LQFP100 is only one pins with DCMI-VSYNC function. There are no more alternative functions pins anywhere on this package.

I can use only LQFP100 version of the MCU. I hope that there is any theory about muxed DCMI-VSYNC and FSMC-NADV functions on this same pin no 93 somethere in documentations? Still ask about help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-29 3:38 AM