- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Why it always takes 12 clock cycle while using the...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Why it always takes 12 clock cycle while using the STLINK to trace single instruction's execution time?(about dual-issue, St-link and Cortex-M7 pipeline)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-22 3:25 AM

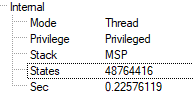

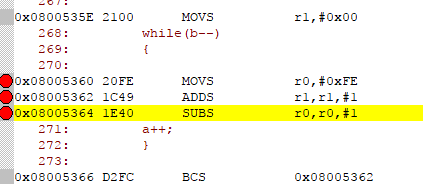

The device is STM32F746NG-DISCO, and I measure the execution time of single instruction by this ways:

int a=0;

int b=255;while(b--)

{ a++; }

make breakpoint and watch the value of States. And by this, I found that for ADD, SUBS, MOV, they are all 12 clock cycles.

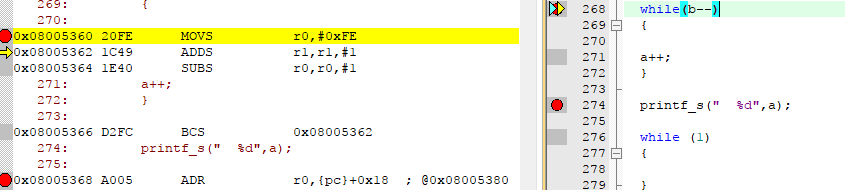

And if I test by this:

It's 423 clock cycles.

I know the cortex-m7 is a dual-issued core but Why the st-link tracer looks a little no accuracy?

So my questions are:

1. If I break the code instruction by instruction, most of the instruction takes 12 clock cycle, how many clock cycles in this is cost by the debugger and tracer? 6 clock cycle? (12 clock cycle - 6 stage pipeline of the instruction = 6 clock cycle)

2. The whole progress is 423 clock cycles (may include 6 clock cycles' debugger latency), could that be calculated out without measuring in debugger?

- Debug STLink GDB Server v.1.3.0 - PARSE ERROR: Argument: -cp in STM32CubeIDE for Visual Studio Code (MCUs)

- Cannot find/enable CMSIS-DSP (arm_math.h) on STM32N6570-DK via STM32CubeMX in STM32CubeMX (MCUs)

- STEVAL-ROBKIT1 (STM32H725 MCU / STM32G071) in Others: STM32 MCUs related

- STM32H745I-DISCO factory reset in STM32 MCUs Boards and hardware tools

- STM32CubeMX2 with TouchGFX in STM32CubeMX2 (MCUs)