Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F0 SPI slave mode issue TXRX HAL

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F0 SPI slave mode issue TXRX HAL

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-01-13 8:24 AM - edited 2023-11-20 9:41 AM

Posted on January 13, 2016 at 17:24

Hi,

I'm using an STM32F0306 in SPI slave mode *** a sub processor in a project. I used cubeMX to generate the initialization and have added functions in Keil v4 The ST part is in slave mode, 8 bit motorola, LSB first , clock pol low, 2nd edge data

void

MX_SPI1_Init(

void

)

{

hspi1.Instance = SPI1;

hspi1.Init.Mode = SPI_MODE_SLAVE;

hspi1.Init.Direction = SPI_DIRECTION_2LINES;

hspi1.Init.DataSize = SPI_DATASIZE_8BIT;

hspi1.Init.CLKPolarity = SPI_POLARITY_HIGH;

hspi1.Init.CLKPhase = SPI_PHASE_2EDGE;

hspi1.Init.NSS = SPI_NSS_SOFT;

hspi1.Init.FirstBit = SPI_FIRSTBIT_LSB;

hspi1.Init.TIMode = SPI_TIMODE_DISABLED;

hspi1.Init.CRCCalculation = SPI_CRCCALCULATION_DISABLED;

hspi1.Init.CRCPolynomial = 7;

hspi1.Init.CRCLength = SPI_CRC_LENGTH_DATASIZE;

hspi1.Init.NSSPMode = SPI_NSS_PULSE_DISABLED;

HAL_SPI_Init(&hspi1);

}1.

for

(uint8_t j=0;j

first byte should be 0x80

1. uint8_t SPI_Buff[28]={ 0x80, 0x2a, 0x2a, 0x2c, /*FIXED*/ 2. 0x00, 0x00, 3. 0x79, 0x7F, 0x7F, 0x7F, /*touch1*/ 4. 0x79, 0x7F, 0x7F, 0x7F, /*touch2*/ 5. 0x79, 0x7F, 0x7F, 0x7F, /*touch3*/ 6. 0x79, 0x7F, 0x7F, 0x7F, /*touch4*/ 7. 0x79, 0x7F, 0x7F, 0x7F, /*touch5*/ 8. 0x63};

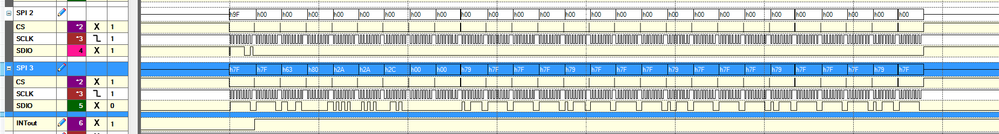

but as can be seen, the data is shift three packets and clearing the DR reg does not fix the issue.

Any hints would be appreciated.

Regards

Robert

#stm32-spi-slave

Any hints would be appreciated.

Regards

Robert

#stm32-spi-slave

Labels:

- Labels:

-

SPI

This discussion is locked. Please start a new topic to ask your question.

1 REPLY 1

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-10 9:18 AM

Sorry, bumping old zombie unanswered threads off my feed

Tips, Buy me a coffee, or three.. PayPal Venmo

Up vote any posts that you find helpful, it shows what's working..

Up vote any posts that you find helpful, it shows what's working..

Related Content

- STM32H753 SPI6 Slave (H7 SPI v2) — Frame qualifies only with NSS-synchronised arming in STM32 MCUs Embedded software

- I2C Slave Address detect. how to code for other peripherals using mfx expander in STM32 MCUs Embedded software

- HAL_I2C_EnableListen_IT() is not enabling Address matched interruption in STM32 MCUs Embedded software

- STM32G4 I2C Slave AF Error on Normal Transaction Completion in STM32 MCUs Embedded software

- STM32H750 SPI errata 2.22.6 workaround – validating delay before SPI disable in low-speed mode in STM32 MCUs Embedded software