- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- SDA held low after slave ACK

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SDA held low after slave ACK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-26 3:07 AM

Hello there,

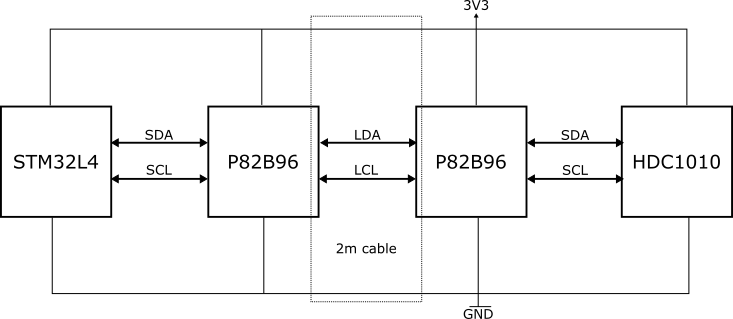

I am working with a system that can be expressed in such block diagram:

This setup works pretty well, but:

- Not on every instance of the device

- Sometimes it stops working, even though it was ok for couple days.

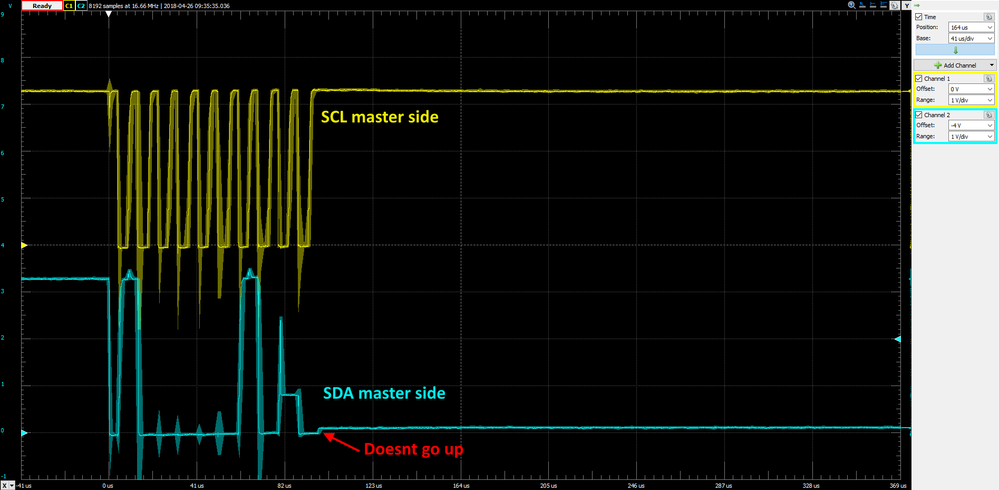

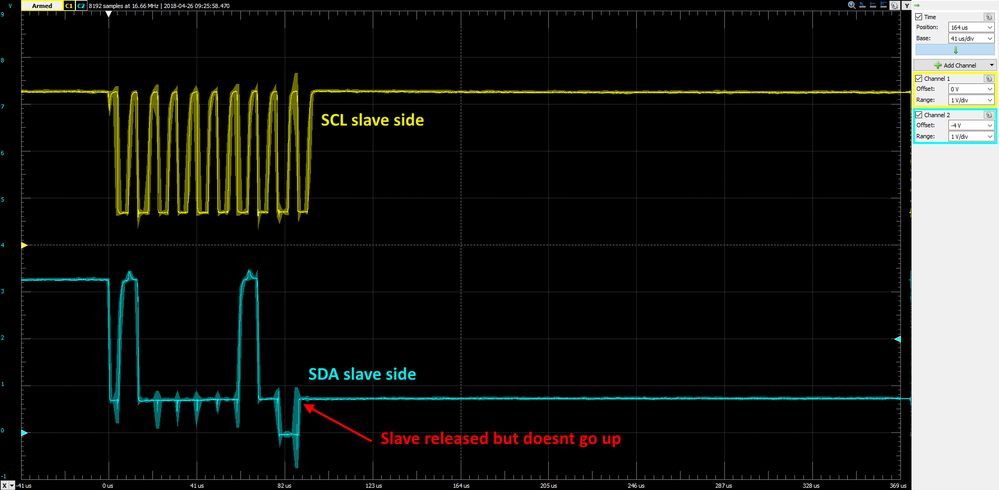

The reason for ''not working'' is that the I2C line become bricked somehow. In order to obtain that state, all I need to do is querry the slave on the other side of I2C buffer for presence. The osc views then look like this:

Master side:

Slave side:

Note: The low level of SDA and SCL is not exatcly 0V, but around 0.7 V as described in P82B96 datasheet.

As you can see from the lower scope view, the slave ACK's (its address is 0x41) and releases the line (one can observe SDA line jump from 0V to 0.7V). The line should be pulled back to VCC but instead its held low, I believe by the master (STM32L4).

I am trying to understand this situation but I cannot figure this out. One things for sure- when the P82B96 I2C buffer is ''shorted'', the system works correctly. Using the buffer somehow interferes with masters I2C data parsing). The worst part is that this doesnt happen always, or starts to happen after a while.

I would appreciate all help in understanding this situation. Are there any cases in which master holds the data line low for some reason? Am I understanding this part correctly?

#buffer #i2c- Labels:

-

I2C

- SPI Comminication between two microcontrollers in STM32 MCUs Embedded software

- STM32G431 Bootloader issue in STM32 MCUs Products

- STM32H753 SPI6 Slave (H7 SPI v2) — Frame qualifies only with NSS-synchronised arming in STM32 MCUs Embedded software

- STM32F4 I2C CR2 Peripheral clock frequency in STM32 MCUs Products

- [STM32H563] [STM32CubeMx] Unable to enable PTP in STM32CubeMX (MCUs)